Functional Description

http://www.motorola.com/computer/literature

2-31

2

.

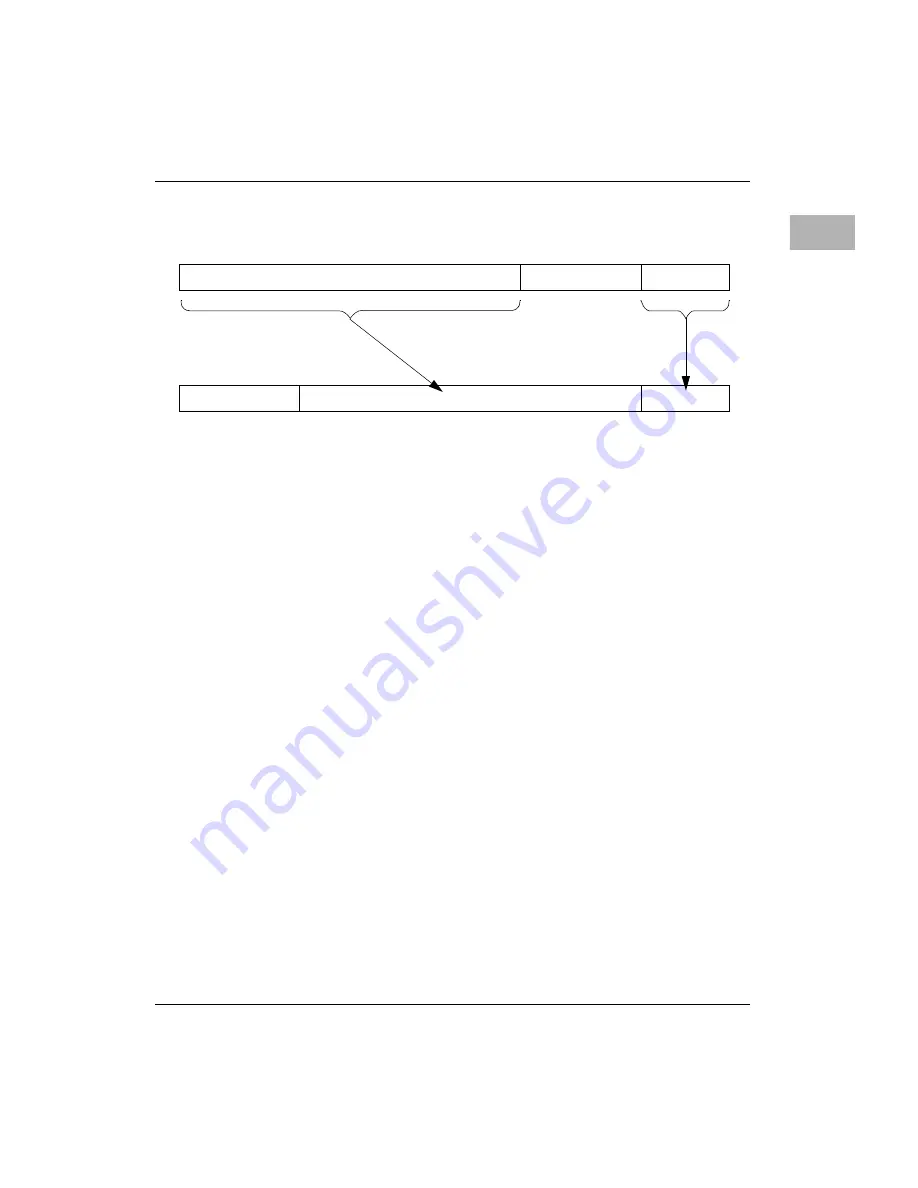

Figure 2-6. PCI Spread I/O Address Translation

Spread I/O addressing allows each PCI device’s I/O registers to reside on

a different PPC memory page, so device drivers can be protected from

each other using memory page protection.

All I/O accesses must be performed within natural word boundaries. Any

I/O access that is not contained within a natural word boundary results in

unpredictable operation. For example, an I/O transfer of four bytes starting

at address $80000010 is considered a valid transfer. An I/O transfer of four

bytes starting at address $80000011 is considered an invalid transfer since

it crosses the natural word boundary at address $80000013/$80000014.

Generating PCI Configuration Cycles

The PHB uses configuration Mechanism #1 as defined in the PCI Local

Bus Specification 2.1 to generate configuration cycles. Please refer to this

specification for a complete description of this function.

Configuration Mechanism #1 uses an address register/data register format.

Performing a configuration access is a two step process. The first step is to

place the address of the configuration cycle within the

CONFIG_ADDRESS register. Note that this action does not generate any

cycles on the PCI bus.

1915 9702

PPC A Offset

31

12 11

5 4

0

31

0

PCI Address

25 24

0 0 0 0 0 0 0

0 0 0 0 0 0 0

5 4

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...