MAX32600 User’s Guide

Communication Peripherals

7.1 I²C

Write 1 to clear.

Set to 1 by hardware when the Rx FIFO is full.

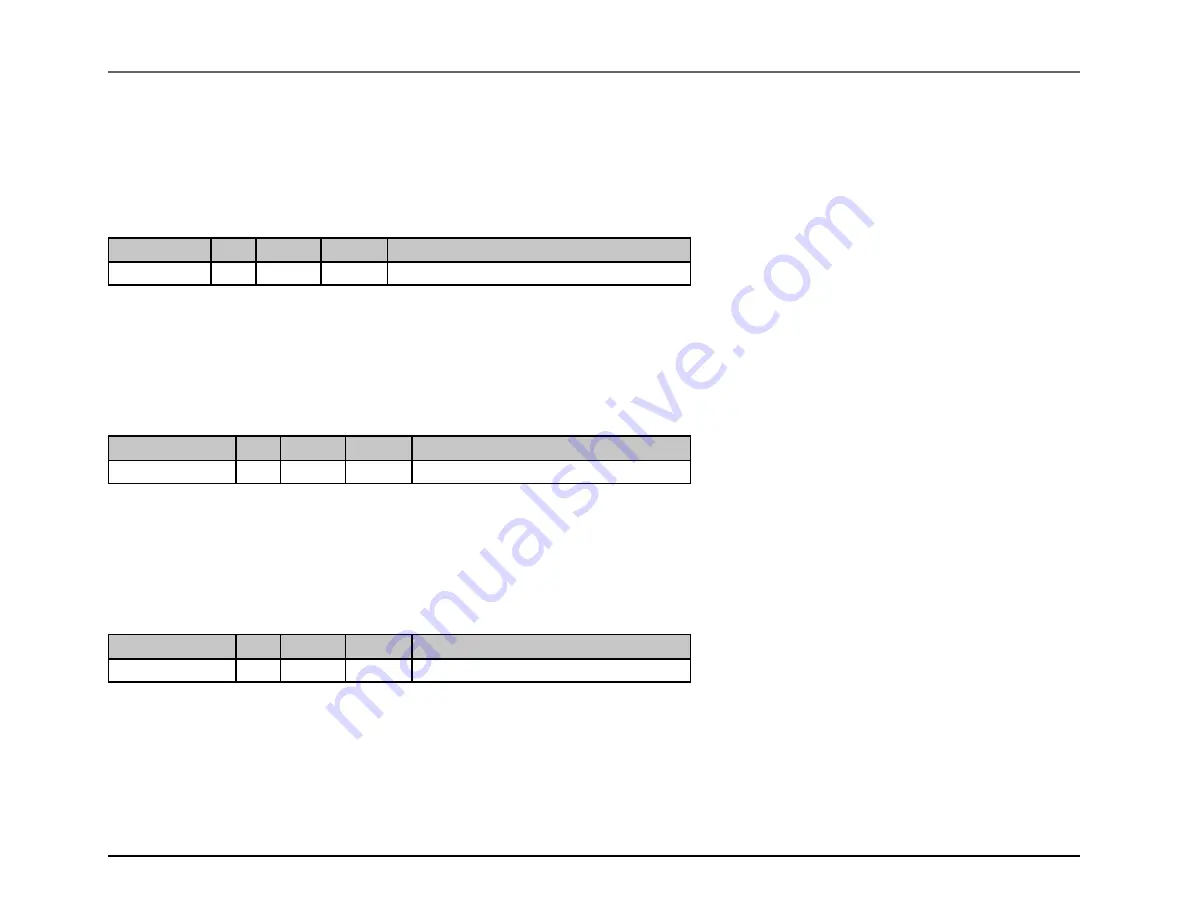

I2CS0_INTFL.rx_clk_stretch

Field

Bits

Default

Access

Description

rx_clk_stretch

7

0

W1C

Rx Clock Stretch Interrupt Status

Write 1 to clear.

Set to 1 by hardware when the I2C slave begins a clock stretch during a receive cycle.

I2CS0_INTFL.tx_clk_stretch_id0

Field

Bits

Default

Access

Description

tx_clk_stretch_id0

8

0

W1C

Tx Clock Stretch (ID0) Interrupt Status

Write 1 to clear.

Set to 1 by hardware when the I2C slave begins a clock stretch during a transmit cycle (ID0).

I2CS0_INTFL.tx_clk_stretch_id1

Field

Bits

Default

Access

Description

tx_clk_stretch_id1

9

0

W1C

Tx Clock Stretch (ID1) Interrupt Status

Write 1 to clear.

Set to 1 by hardware when the I2C slave begins a clock stretch during a transmit cycle (ID1).

I2CS0_INTFL.restart_id0

Rev.1.3 April 2015

Maxim Integrated

Page 248