MAX32600 User’s Guide

System Clock, Timers/Counters, Watchdog Timers and Real Time Clock

10.2 Watchdog Timers

Write 1 to clear this flag to 0.

Set to 1 by hardware when the watchdog timer reaches the end of the reset period without being cleared.

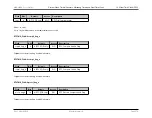

10.2.5.1.4

WDTn_ENABLE

WDTn_ENABLE.timeout

Field

Bits

Default

Access

Description

timeout

0

0

R/W

Enable Watchdog Interrupt

• 0: No interrupt will be triggered when the Watchdog Interrupt Flag is set.

• 1: An interrupt will be triggered by the WDT when the Watchdog Interrupt Flag is set to 1.

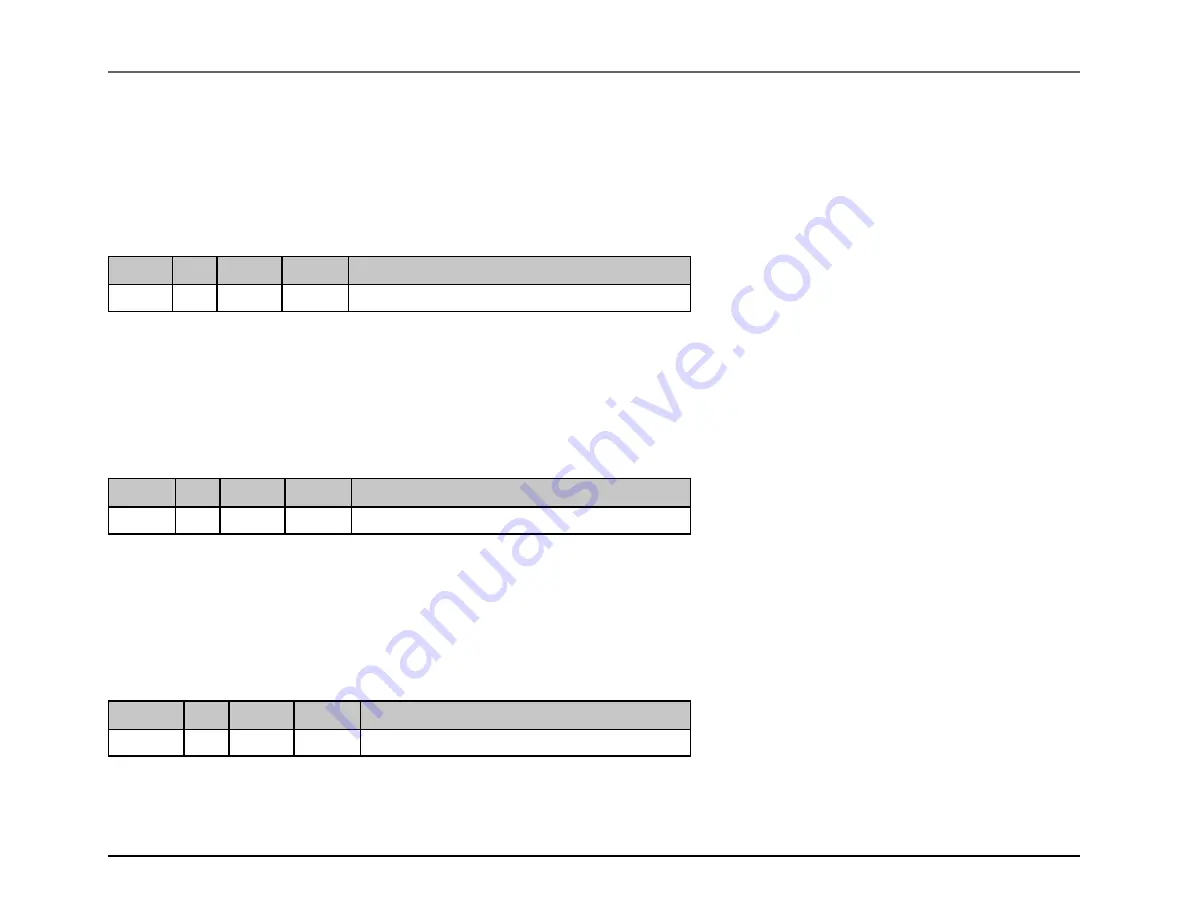

WDTn_ENABLE.pre_win

Field

Bits

Default

Access

Description

pre_win

1

0

R/W

Enable Watchdog Pre-Window Reset Interrupt

• 0: No pre-window reset interrupt will be triggered.

• 1: An interrupt will be triggered when the Pre-Window Reset Interrupt Flag is set to 1.

WDTn_ENABLE.reset_out

Field

Bits

Default

Access

Description

reset_out

2

0

R/W

Enable Watchdog Reset Output

• 0: No reset will be triggered by this watchdog.

• 1: A system reset (for WDT0) or system reboot (for WDT1) will be triggered when the Watchdog Reset Flag is set to 1.

Rev.1.3 April 2015

Maxim Integrated

Page 562