MAX32600 User’s Guide

Introduction

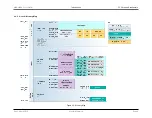

2.2 Core and Architecture

2.2.3

AHB Buses

The standard ARM Advanced High Performance Bus (AHB-Lite version) is used for several different system bus masters on the

MAX32600

. All buses are 32-bits in

width.

•

I-Code

: Performs instruction fetches from internal code memory regions. On the

MAX32600

, accesses to internal program flash memory (for instruction

decoding purposes) are cached to improve execution throughput.

•

D-Code

: Performs data fetches from program flash memory; this includes literal local constant fetches. These data fetches are not cached, unlike instruction

code fetches.

•

System

: Performs data read/write and bit-band operations on internal SRAM, and data read/write operations on peripherals (including bit-band operations)

and vendor defined expansion devices in the system area.

Note

Bit-band operations are translated internally by the ARM core into a read-modify-write sequence. Only the core itself (when performing instruction

execution) can read or write to locations using the bit-banding function. The bit-banding alias areas, although they are shown on the memory map,

do not exist as separate logical mapped areas; they cannot be accessed by other AHB masters (e.g., the DMA master or the JTAG/PTP master),

since they do not exist at this layer.

2.2.4

APB Buses

The External PPB (private peripheral bus) is a 32-bit bus based on the APB (Advanced Peripheral Bus) standard. It is intended for adding components to the private

peripheral bus area which are not intended for general application use, since privileged operating mode is required to access this area. The

MAX32600

does not

currently map any non-core components to this bus area.

The majority of the digital and analog peripherals on the

MAX32600

are controlled by registers that are memory mapped into the Peripheral region from address

0x4000_0000 to 0x400F_FFFF (in the bit-banding enabled region). These peripherals are connected to the CPU core using a lower-speed APB peripheral bus

(connected to the System AHB-Lite bus through an AHB-to-APB bridge).

Peripherals which require higher speed access for large data transfers have control/buffer regions mapped to the AHB bus from address 0x4010_0000 to 0x401F_

−

FFFF. These regions are designed to allow more rapid data transfer directly through the AHB bus, without having to go through the AHB-to-APB bridge. Peripherals

using this type of interface include SPI, I

2

C, DAC, ADC, AES, Micro MAA, CRC and USB.

2.2.5

Nested Vectored Interrupt Controller (NVIC)

The

MAX32600

includes the standard Nested Vectored Interrupt Controller (NVIC) as implemented for the Cortex-M3 ARM core. The NVIC supports high-speed,

deterministic interrupt response, interrupt masking, and multiple interrupt sources. External interrupts support rising or falling edge trigger mode as well as level

triggered mode.

Rev.1.3 April 2015

Maxim Integrated

Page 9