S1R72803F00A

60

EPSON

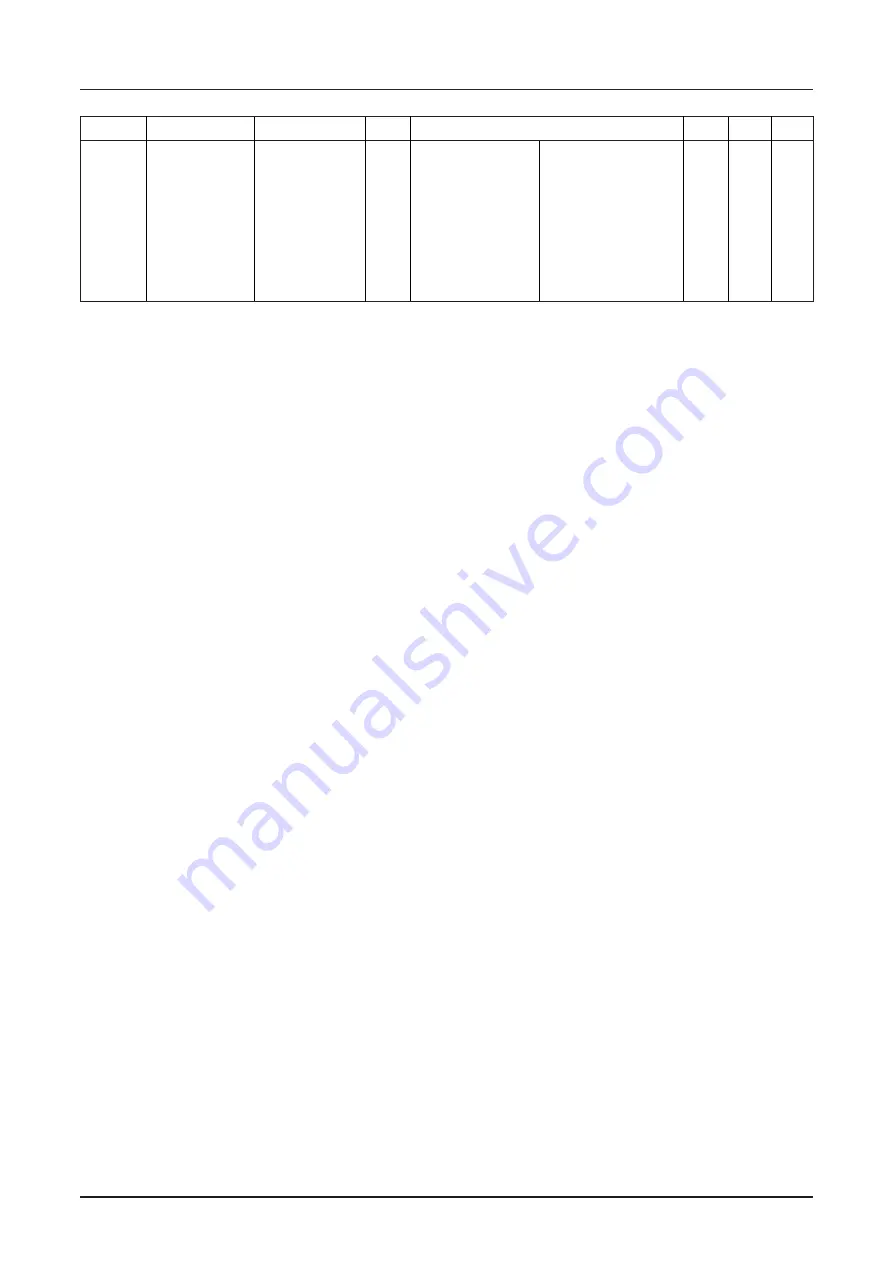

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x30

HwSBP2Ctl

7: PtNotPresent

R/W

0: Present

1: Not Present

6: HOSTtoDev

R/W

0: Host <– Device

1: Host –> Device

5: FromStream

R/W

0: From PageTable 1: FromStream

4: LastPT

R/W

0: None

1: Ignore

0x00

0x00

–

3: HwSBP2Rst

W

0: None

1: Reset

2: HwSBP2Rsum

W

0: None

1: Resume

1: HwSBP2Pause

W

0: None

1: Pause

0: HwSBP2Start

W

0: None

1: Start

Hardware SBP2 Control Register

This register controls the SBP2 processing of this IC.

Bit7 UltraDmaMode

PtNotPresent:0 (Present) Set => PageTable exists.

PtNotPresent:1 (Not Present) Set => PageTable does not exist.

Bit6 HOSTtoDev

HOSTtoDev:0 (Host<-Device) Set => Transfers data from Device to Host.

HOSTtoDev:1 (Host->Device) Set => Transfers data from Host to Device.

Bit5 FromStream

FromStream:0 (FromPt) Set => Starts with the PageTable Processing.

FromStream:1 (FromStream) Set => Starts with the Stream processing.

Bit4 LastPT

This bit indicates the 0x32 bit 3 NotQuad status and specifies whether to generate an interrupt if SegmentLength

of the last PageTableElement on PageTable is not the Quad unit during the HwSBP2 process.

LastPT: 0 (None) Set => The NotQuad status is indicated for the last PageTableElement and an interrupt is

generated.

LastPT: 1 (Ignore) Set => The NotQuad status is not indicated for the last PageTableElement and an interrupt

is not generated.

Bit3 HwSBP2Rst

SBP2Reset:1 (Reset) Set => Resets the hwSBP2.

If you read it, it indicates 0.

Bit2 HwSBP2Rsum

SBP2Resume:1 (Reset) Set => Resumes the hwSBP2 processing in pause.

If you read it, it indicates 0.

Bit1 HwSBP2Pause

SBP2Pause:1 (Pause) Set => Pauses the hwSBP2 processing in execution.

If you read it, it indicates 0.

Bit0 HwSBP2Start

SBP2Start:1 (Start) Set => Starts the hwSBP2 processing.

If you read it, it indicates 0.