S1R72803F00A

EPSON

83

IDE DMA Status Register

This register indicates the status of the DMA of the IDE interface.

Bit7::5 FIFOCnt[2:0]

This bit indicates the number of words in the FIFO.

Bit4::2 Reserved

Bit1 DmaPause

Indicates whether the DMA mode in execution is in pause status or not. It is enabled when the DmaRun bit is

“1”.

DmaPause:1 DMA is in pause.

DmaPause:0 DMA is in execution.

Bit0 DmaRun

Indicates whether the DMA mode in execution is in execution or not. It is enabled when the DmaRun bit is “1”.

DmaPause:1 DMA is in execution.

DmaPause:0 DMA is not in execution.

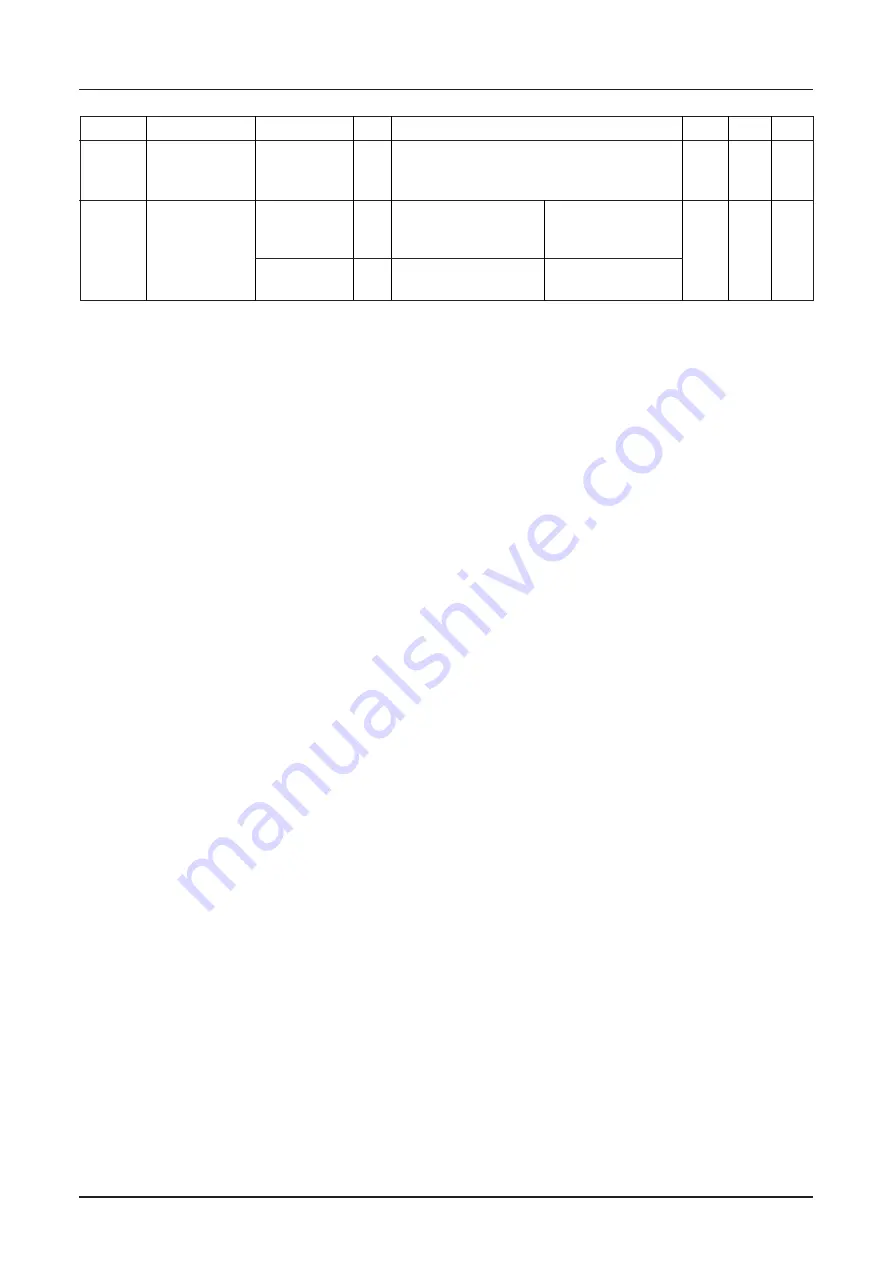

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x67

IDE_DmaStat

7: FIFOCnt[2]

R

6: FIFOCnt[1]

R

Indecate word count in FIFO

5: FIFOCnt[0]

R

4:

0:

1:

0x00

0x00

–

3:

0:

1:

2:

0:

1:

1: DmaPause

R

0: IDE DMA not Pause 1: IDE DMA Pause

0: DmaRun

R

0: Not DMA

1: IDE DMA Running