6-2

RANGE REGISTERS

writethrough. The memory types are defined for specific address ranges based on range regis-

ters. The memory types currently defined, are shown in Table 6-1. The Pentium Pro processor

drives the memory type to the Pentium Pro processor bus in the second clock of the Request

Phase on the ATTR[3:0]# (attribute) pins.

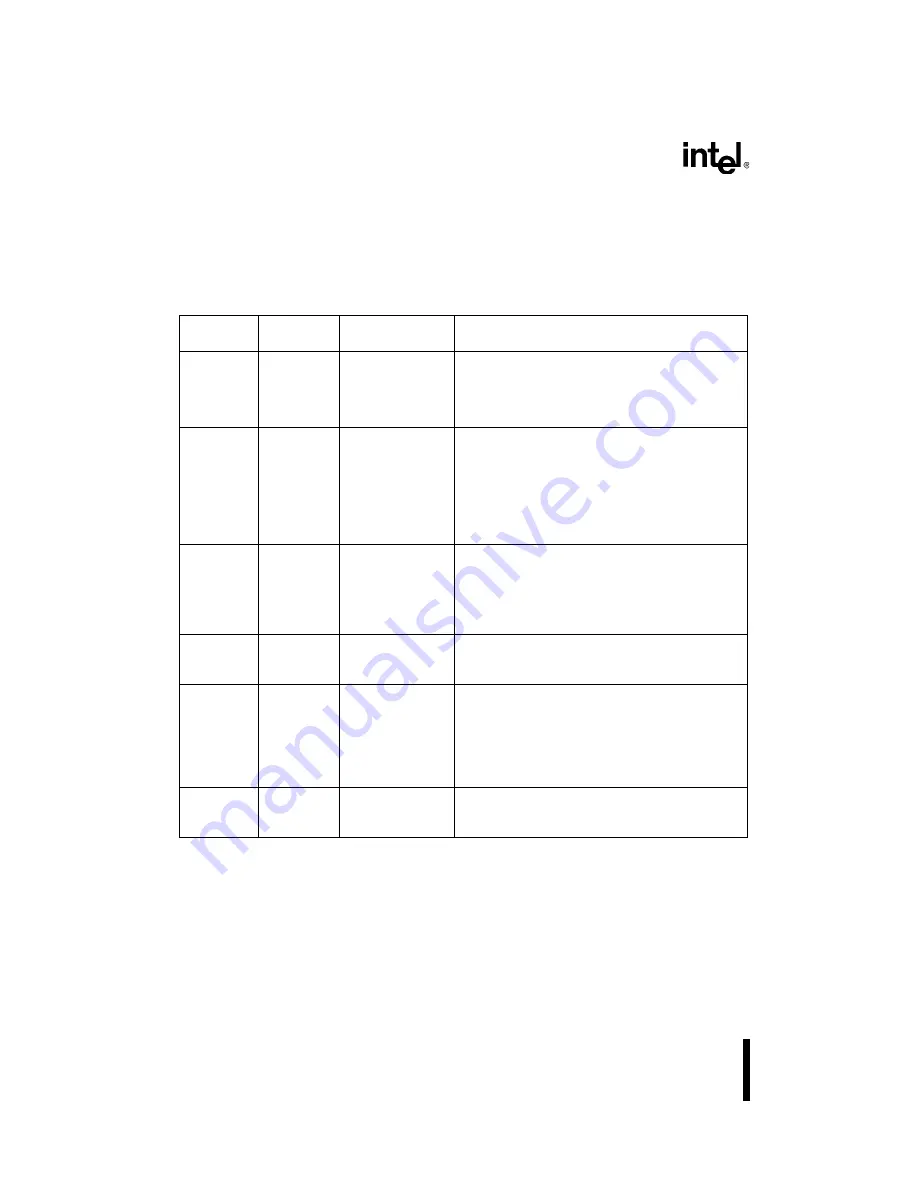

Table 6-1. Pentium

®

Pro Processor Architecture Memory Types

ATTR[7:0]#

Encoding

Mnemonic

Name

Description

00000000

UC

uncacheable

Not cached. All reads and writes appear on the bus.

Reads and writes can have side effects, therefore no

speculative accesses are made to UC memory.

UC memory is useful for memory-mapped I/O.

00000100

WC

write-combining

Reads are not cached. Writes can be delayed and

combined. They are also weakly ordered resulting in

substantially higher write throughput. Reading WC

memory cannot have side effects and speculative

reads are allowed.

WC memory is useful for applications such as linear

frame buffers.

00000101

WT

write-through

Cacheable memory for which all writes are written

through to main memory.

Writing WT memory never causes a cache fill of an

invalid cache line and either invalidates or updates a

valid cache line.

00000110

WP

write-protected

Cacheable memory for which reads can hit the cache

and read misses cause cache fills, but writes bypass

the cache entirely.

00000111

WB

writeback

Cacheable memory for which write misses allocate

cache lines and writes are performed entirely in the

cache whenever possible.

WB memory is useful for normal memory, providing

the best performance and the least bus traffic for

many applications.

All others

—

Reserved

Attempting to write a reserved value into a memory

type field of an MTRR signals a #GP(0) fault and

does not update the MTRR.

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......