4-29

BUS PROTOCOL

4.5.2.3.

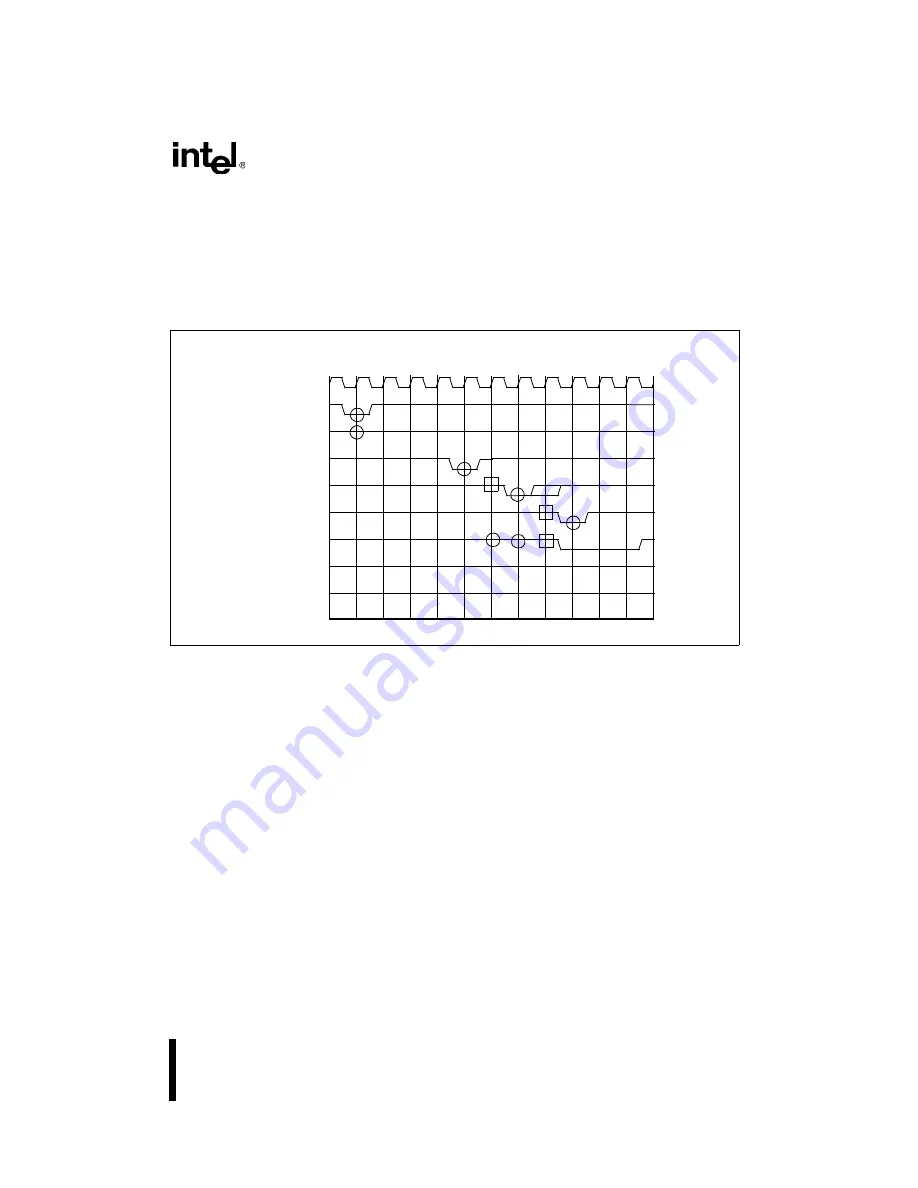

IMPLICIT WRITEBACK ON A READ TRANSACTION

Figure 4-16 shows a read transaction with an implicit writeback. TRDY# is asserted in this op-

eration because there is writeback data to transfer. Note that the implicit writeback response

must be asserted exactly one clock after valid TRDY# assertion is sampled. That is, TRDY# is

sampled active and DBSY# is sampled inactive.

A transaction is issued in T1. The REQa0# pin indicates a read transaction, so TRDY# is as-

sumed not needed for this transaction.

But snoop results observed in T6 indicate that an implicit writeback will occur (HITM# is as-

serted), therefore a TRDY# assertion is needed. Since the response for the previous transaction

is complete, and no request initiated TRDY# assertion is needed, TRDY# for the implicit write-

back is asserted in T7. (TRDY# assertion due to an implicit writeback is called a snoop initiated

TRDY#.) Since DBSY# is observed inactive in T7, TRDY# can be deasserted in one clock in

T8, but need not be deasserted until the response is driven on RS[2:0]#.

In T9, one clock after the observation of active TRDY# with inactive DBSY# for the implicit

writeback, the Implicit Writeback Response must be driven on RS[2:0]# and the data is driven

on the data bus. This makes the data transfer and response behave like both a read (for the re-

questing agent) and a write (for the addressed agent).

Figure 4-16. RS[2:0]# Activation with Snoop Initiated TRDY#

CLK

DBSY#

TRDY#

HITM#

RS[2:0]#

{scnt}

1

2

3

4

5

6

7

8

9

10

11

12

ADS#

{rcnt}

REQ0#

0

0

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......