9-16

DSP56367

MOTOROLA

Serial Host Interface

Serial Host Interface Programming Model

Note:

Programmers should take care to ensure that all DMA channel service to HTX is

disabled before setting HIDLE.

9.5.6.9

HCSR Bus-Error Interrupt Enable (HBIE)—Bit 10

The read/write control bit HBIE is used to enable the SHI bus-error interrupt. If HBIE is

cleared, bus-error interrupts are disabled, and the HBER status bit must be polled to determine

if an SHI bus error occurred. If both HBIE and HBER are set, the SHI requests an SHI

bus-error interrupt service from the interrupt controller. HBIE is cleared by hardware reset

and software reset.

Note:

Clearing HBIE masks a pending bus-error interrupt only after a one instruction

cycle delay. If HBIE is cleared in a long interrupt service routine, it is

recommended that at least one other instruction separate the instruction that clears

HBIE and the RTI instruction at the end of the interrupt service routine.

9.5.6.10

HCSR Transmit-Interrupt Enable (HTIE)—Bit 11

The read/write control bit HTIE is used to enable the SHI transmit data interrupts. If HTIE is

cleared, transmit interrupts are disabled, and the HTDE status bit must be polled to determine

if HTX is empty. If both HTIE and HTDE are set and HTUE is cleared, the SHI requests an

SHI transmit-data interrupt service from the interrupt controller. If both HTIE and HTUE are

set, the SHI requests an SHI transmit-underrun-error interrupt service from the interrupt

controller. HTIE is cleared by hardware reset and software reset.

Note:

Clearing HTIE masks a pending transmit interrupt only after a one instruction

cycle delay. If HTIE is cleared in a long interrupt service routine, it is

recommended that at least one other instruction separate the instruction that clears

HTIE and the RTI instruction at the end of the interrupt service routine.

9.5.6.11

HCSR Receive Interrupt Enable (HRIE[1:0])—Bits 13–12

The read/write control bits HRIE[1:0] are used to enable the SHI receive-data interrupts. If

HRIE[1:0] are cleared, receive interrupts are disabled, and the HRNE and HRFF (bits 17 and

19, see below) status bits must be polled to determine if there is data in the receive FIFO. If

HRIE[1:0] are not cleared, receive interrupts are generated according to Table 9-6. HRIE[1:0]

are cleared by hardware and software reset.

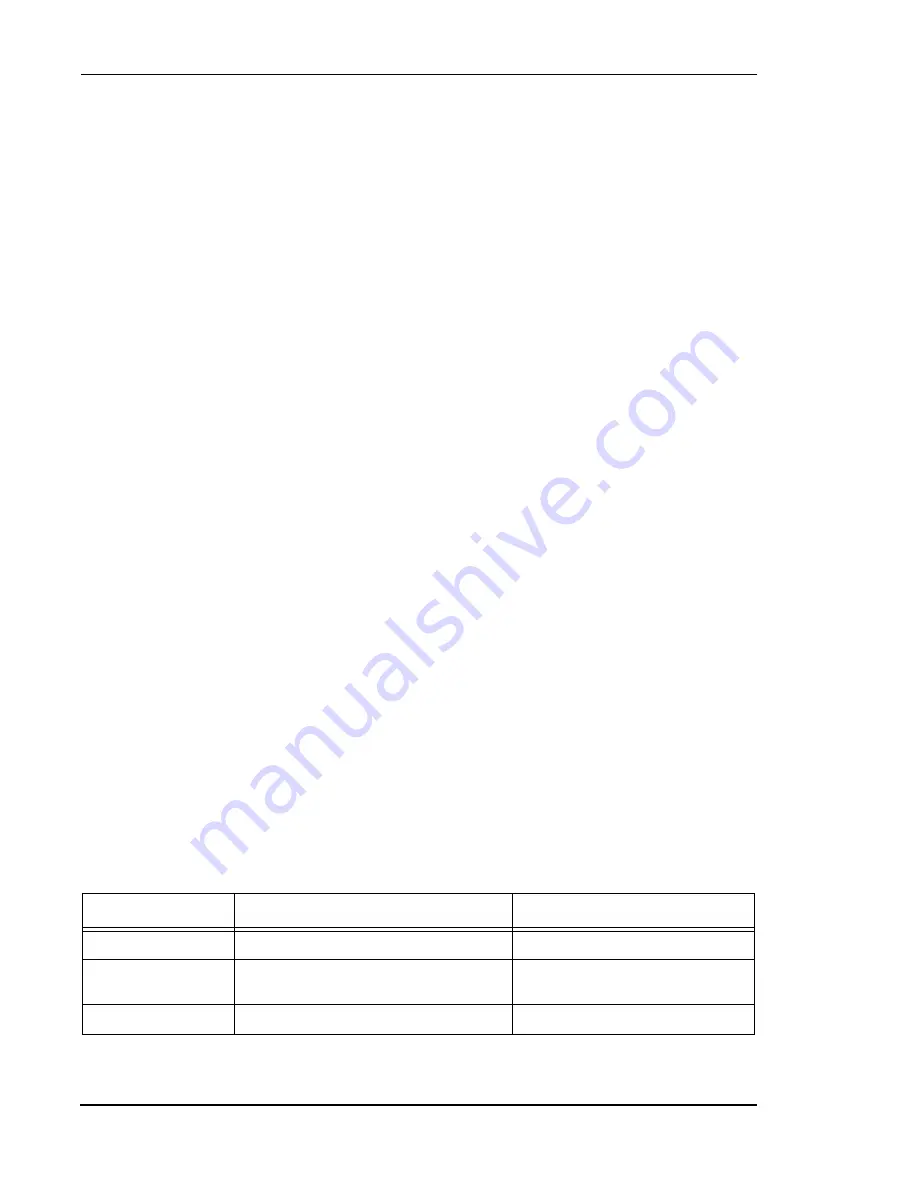

Table 9-6 HCSR Receive Interrupt Enable Bits

HRIE[1:0]

Interrupt

Condition

00

Disabled

Not applicable

01

Receive FIFO not empty

Receive Overrun Error

HRNE = 1 and HROE = 0

HROE = 1

10

Reserved

Not applicable

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......