Rev. 3.0, 03/01, page 249 of 390

Section 17 PS/2 Interface

17.1

Overview

The PS/2 interface is implemented as a Register Interface peripheral. All protocols and timing

conform to IBM-PC PS/2 specifications. The interface supports two emulation channels to be

connected PS/2 keyboard and PS/2 mouse individually.

17.2

Pin Configuration

Pin Number

Pin Name

I/O

Description

C22

KBCK

IO

Keyboard clock input/output

B22

KBDATA

IO

Keyboard data input/output

A22

MSCK

IO

Mouse clock input/output

D21

MSDATA

IO

Mouse data input/output

17.3

Registers Description

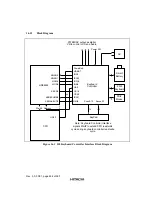

Table 17-1 lists the control registers used by the PS/2 interface. All control registers are 16 bits

wide, are aligned to 4-byte boundaries, and control various aspects of the system. These may only

be read and written as 16 bit words. Control registers are located in the 0x1000DC00-0x1000DC18

block of the physical address space.

Table 17.1

PS/2 Interface Control Registers

Name

Address

Register Size

Access Size

Keyboard Control/status register(KBCSR)

H'1000DC00

16 bits

16 bits

Keyboard interrupt status register(KBISR)

H'1000DC04

16 bits

16 bits

Mouse Control/status register(MSCSR)

H'1000DC10

16 bits

16 bits

Mouse interrupt status register(MSISR)

H'1000DC14

16 bits

16 bits

Summary of Contents for HD64465

Page 25: ...Rev 3 0 03 01 page 6 of 390 ...

Page 59: ...Rev 3 0 03 01 page 40 of 390 ...

Page 97: ...Rev 3 0 03 01 page 78 of 390 ...

Page 147: ...Rev 3 0 03 01 page 128 of 390 ...

Page 199: ...Rev 3 0 03 01 page 180 of 390 ...

Page 247: ...Rev 3 0 03 01 page 228 of 390 ...

Page 385: ...Rev 3 0 03 01 page 366 of 390 ...

Page 389: ...Rev 3 0 03 01 page 370 of 390 ...

Page 409: ...Rev 3 0 03 01 page 390 of 390 ...