10-20

DS785UM1

Copyright 2007 Cirrus Logic

DMA Controller

EP93xx User’s Guide

1

0

1

0

10

During normal operation, using the “fair” rotating priority scheme shown in

, the last

channel to be serviced becomes the lowest priority channel with the others rotating

accordingly. In addition, any device requesting service is guaranteed to be recognized after

no more than eleven higher priority services has occurred. This prevents any one channel

from monopolizing the system. When the bus is idle, the scheme reverts to a fixed priority

whereby the highest priority request gets in first (as shown in

resumes to normal operation.

In the case where the two M2M channels are requesting a service, the [PW] size of the read

or write transfers for the first channel are completed before the read transfer for the second

channel begins. See subsections under

for detailed information about

handshaking protocols for hardware and software-triggered M2M channel transfers.

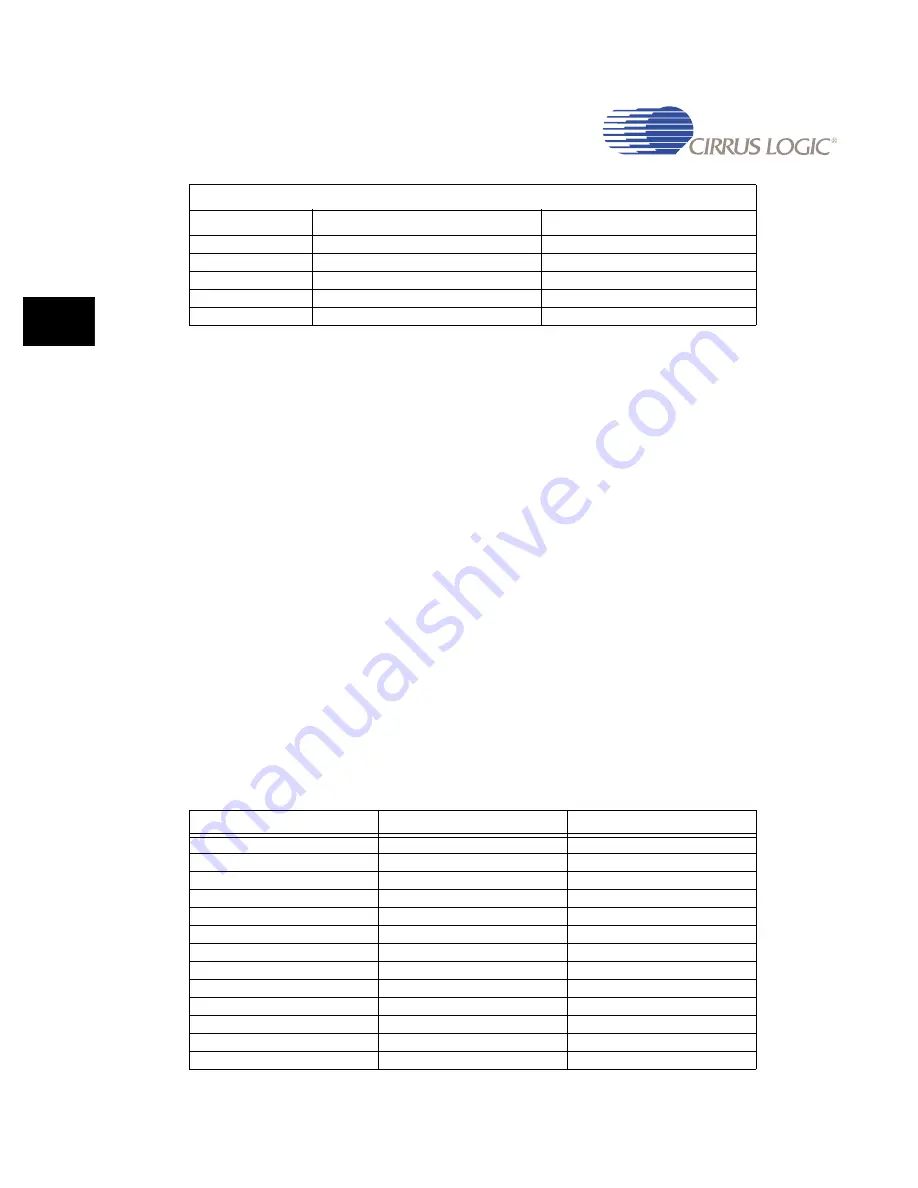

10.2 Registers

10.2.1 DMA Controller Memory Map

defines the DMA Controller mapping for each of 10 M2P (memory-to-peripheral)

channels (5 Tx and 5 Rx), plus the 2 M2M (memory-to-memory) channels.

Before programming a channel, the clock for that channel must be turned on by setting the

appropriate bit in the PwrCnt register of the Clock and State Controller block.

M2P Ch 7

M2P Ch 5

M2P Ch 8

M2P Ch 6

M2P Ch 9

M2P Ch 7

M2M Ch 0

M2P Ch 8

Lowest

M2M Ch 1

M2P Ch 9

Table 10-3. DMA Memory Map

ARM920T Address

Description

Channel Base Address

0x8000_0000 -> 0x8000_003C

M2P Channel 0 Registers (Tx)

0x8000_0000

0x8000_0040 -> 0x8000_007C

M2P Channel 1 Registers (Rx)

0x8000_0040

0x8000_0080 -> 0x8000_00BC

M2P Channel 2 Registers (Tx)

0x8000_0080

0x8000_00C0 -> 0x8000_00FC

M2P Channel 3 Registers (Rx)

0x8000_00C0

0x8000_0100 -> 0x8000_013C

M2M Channel 0 Registers

0x8000_0100

0x8000_0140 -> 0x8000_017C

M2M Channel 1 Registers

0x8000_0140

0x8000_0180 -> 0x8000_01BC

Not Used

0x8000_01C0 -> 0x8000_01FC

Not Used

0x8000_0200 -> 0x8000_023C

M2P Channel 5 Registers (Rx)

0x8000_0200

0x8000_0240 -> 0x8000_027C

M2P Channel 4 Registers (Tx)

0x8000_0240

0x8000_0280 -> 0x8000_02BC

M2P Channel 7 Registers (Rx)

0x8000_0280

0x8000_02C0 -> 0x8000_02FC

M2P Channel 6 Registers (Tx)

0x8000_02C0

0x8000_0300 -> 0x8000_033C

M2P Channel 9 Registers (Rx)

0x8000_0300

Table 10-2. M2P DMA Bus Arbitration (Continued)

Internal Arbitration Priority

CHARB = 0

CHARB = 1

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...