Exceptions

5-30

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

Table 5-11 shows debug faults.

5.12.3

Fault status registers and fault address registers

Each fault has a fault status register with a flag for that fault.

There are:

•

three configurable fault status registers that correspond to the three configurable

fault handlers

•

one hard fault status register

•

one debug fault status register.

Depending on the cause, one of the five status registers has a bit set.

There are two

Fault Address Registers

(FAR):

•

Bus Fault Address Register

(BFAR)

•

Memory Fault Address Register

(MFAR).

A flag in the corresponding fault status register indicates when the address in the fault

address register is valid.

Note

BFAR and MFAR are the same physical register. Because of this, the BFARVALID and

MFARVALID bits are mutually exclusive.

Table 5-12 on page 5-31 shows the fault status registers and two fault address registers.

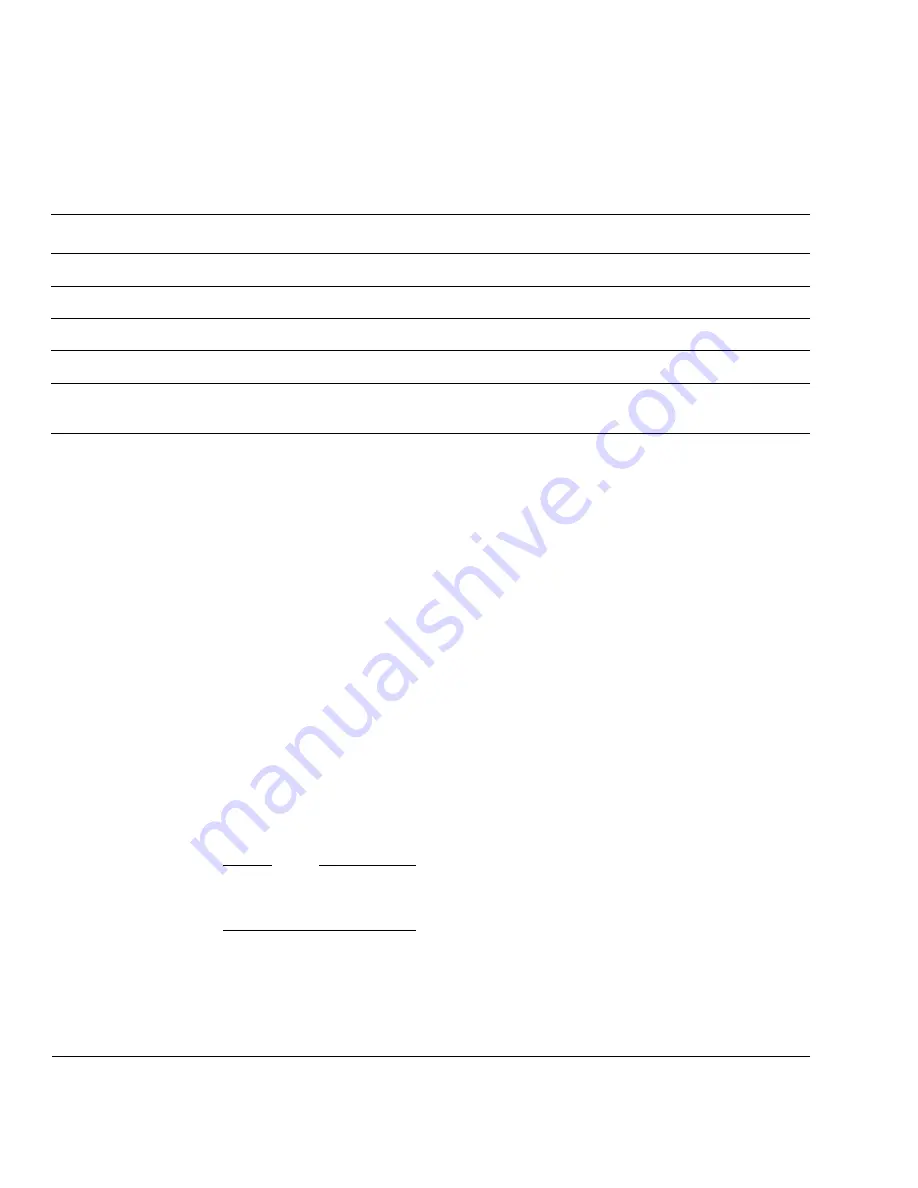

Table 5-11 Debug faults

Fault

Flag

Notes

Trap enable bit

Internal halt request

HALTED

NVIC request from, for example, step, core halt

-

Breakpoint

BKPT

SW breakpoint from patched instruction or FPB

-

Watchpoint

DWTTRAP

Watchpoint match in DWT

-

External

EXTERNAL

EDBGRQ line asserted

-

Vector catch

VCATCH

Vector catch triggered. Corresponding FSR contains the

primary cause of the exception.

VC_xxx bit(s) or

RESETVCATCH set