Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-9

Unrestricted Access

Non-Confidential

Table 8-3 describes the bit assignments of the Auxiliary Control Register.

SysTick Control and Status Register

Use the SysTick Control and Status Register to enable the SysTick features.

The register address, access type, and Reset state are:

Address

0xE000E010

Access

Read/write

Reset state

0x00000000

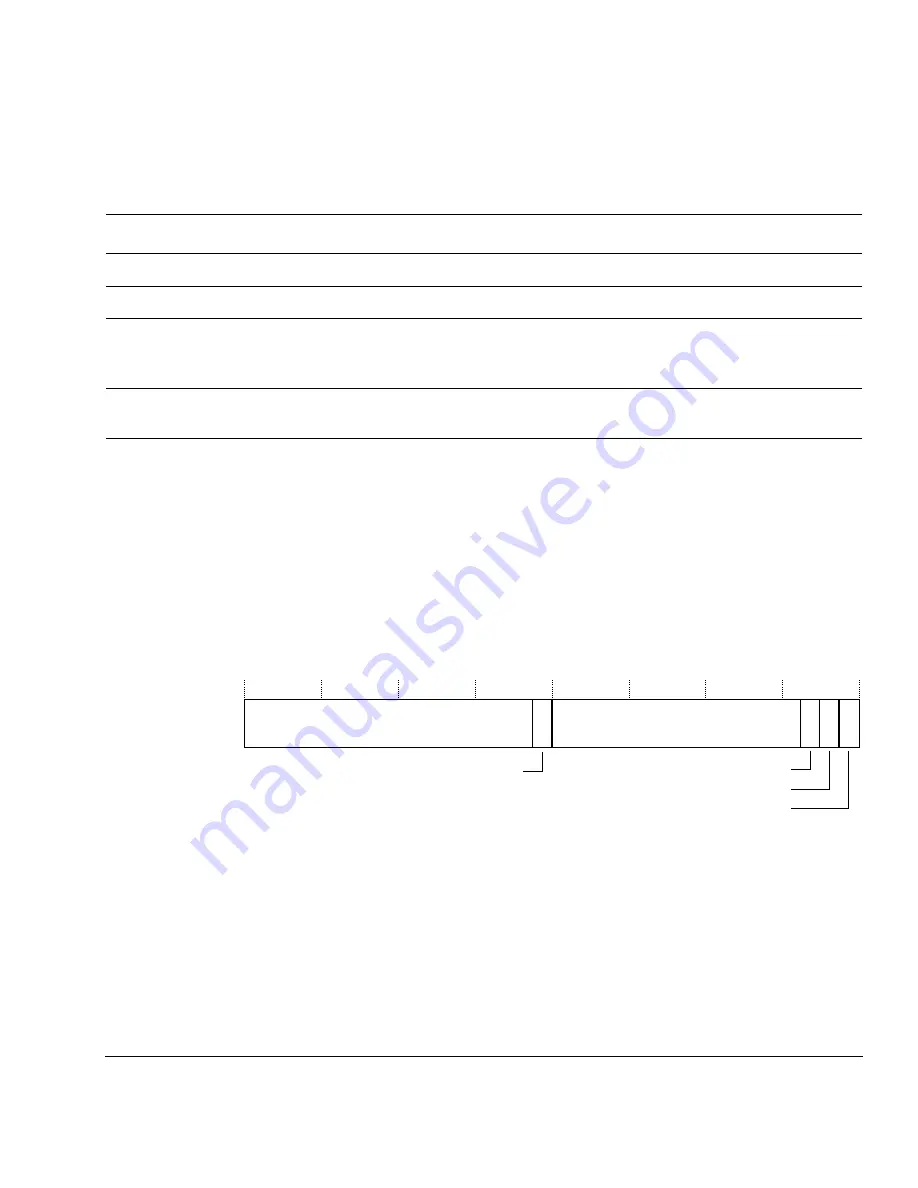

Figure 8-3 shows the bit assignments of the SysTick Control and Status Register.

Figure 8-3 SysTick Control and Status Register bit assignments

Table 8-3 Auxiliary Control Register bit assignments

Bits

Field

Function

[31:3]

-

Reserved

[2]

DISFOLD

Disables IT folding.

[1]

DISDEFWBUF

Disables write buffer use during default memory map accesses. This causes all bus faults to

be precise bus faults but decreases the performance of the processor because the stores to

memory have to complete before the next instruction can be executed.

[0]

DISMCYCINT

Disables interruption of multi-cycle instructions. This increases the interrupt latency of the

processor because LDM/STM completes before interrupt stacking occurs.

31

0

Reserved

Reserved

16 15

17

COUNTFLAG

1

2

CLKSOURCE

TICKINT

ENABLE