Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-23

Unrestricted Access

Non-Confidential

The register address, access type, and Reset state are:

Address

0xE000ED0C

Access

Read/write

Reset state

0x00000000

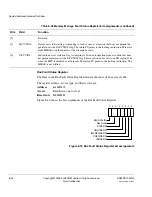

Figure 8-11 shows the bit assignments of the Application Interrupt and Reset Control

Register.

Figure 8-11 Application Interrupt and Reset Control Register bit assignments

Table 8-17 describes the bit assignments of the Application Interrupt and Reset Control

Register.

31

16 15

0

VECTKEY/VECTKEYSTAT

1

2

Reserved

14

PRIGROUP

Reserved

11

8

10

7

ENDIANESS

VECTCLRACTIVE

VECTRESET

3

SYSRESETREQ

Table 8-17 Application Interrupt and Reset Control Register bit assignments

Bits

Field

Function

[31:16]

VECTKEY

Register key. Writing to this register requires

0x5FA

in the VECTKEY field. Otherwise

the write value is ignored.

[31:16]

VECTKEYSTAT

Reads as

0xFA05

.

[15]

ENDIANESS

Data endianness bit:

1 = big endian

0 = little endian.

ENDIANESS is sampled from the BIGEND input port during reset. You cannot change

ENDIANESS outside of reset.

[14:11]

-

Reserved

[10:8]

PRIGROUP

Interrupt priority grouping field: