Bus Interface

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

12-9

Unrestricted Access

Non-Confidential

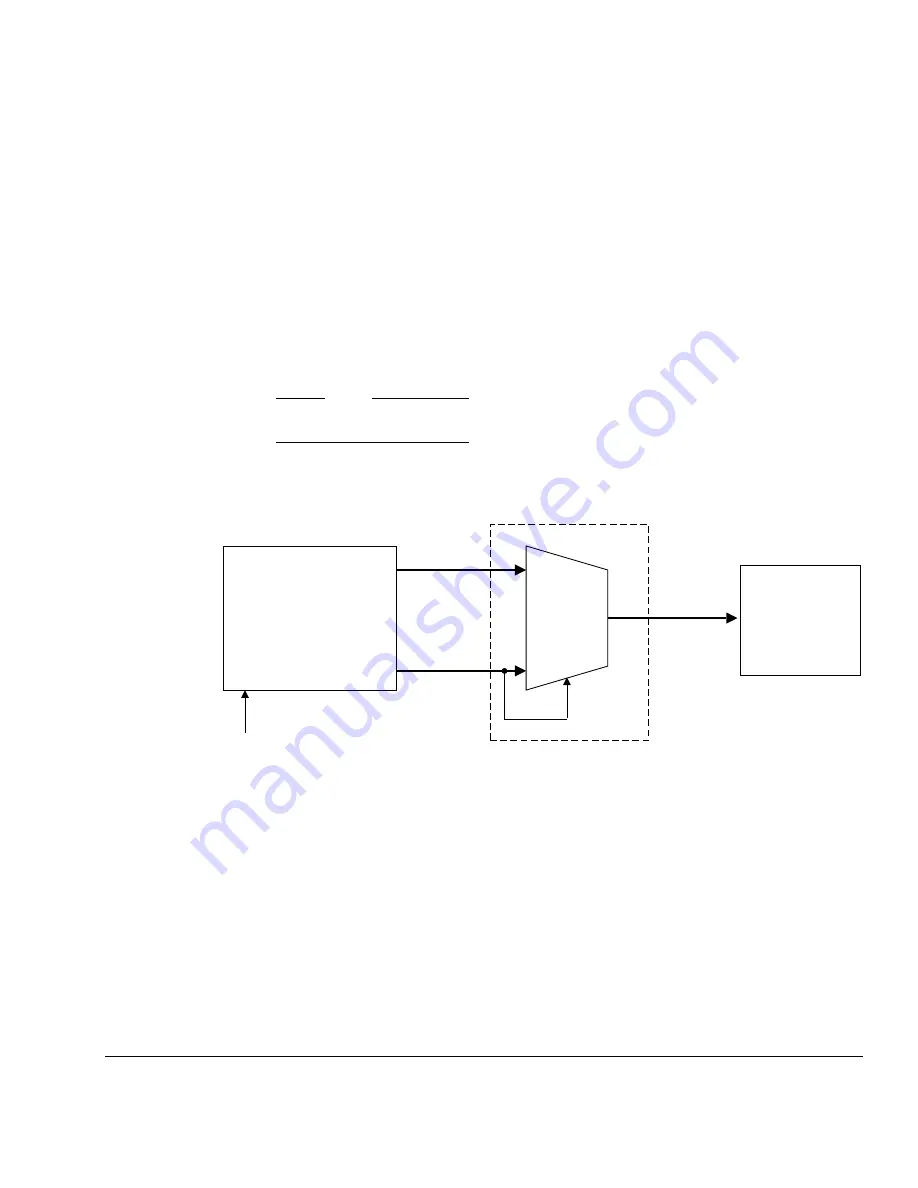

12.6

Unifying the code buses

For some systems you might want to combine the processor core’s ICode and DCode

buses into a single, unified Code bus. To support this for high-speed operation, the

processor has the

DNOTITRANS

input that suppresses the

HTRANSI

line when

HTRANSD

becomes active. With

DNOTITRANS

asserted, if

HTRANSI

and

HTRANSD are to be active simultaneously in corresponding single-cycle address

phases, then only

HTRANSD

is asserted. The ICode transaction is waited internal to

the processor. In other words, the external ICode bus is forced into an idle state. The two

HTRANS

signals are therefore guaranteed never to be simultaneously active, which

permits the bus multiplexer to be a very simple device.

Note

DNOTITRANS

is a static input that must be tied high to enforce this behavior.

The external ICode/DCode bus multiplexer can be integrated into a Cortex-M3 system

as Figure 12-1 shows.

Figure 12-1 ICode/DCode multiplexer

Cortex-M3

ICode

DCode

AHBI

AHBD

AHBC

Memory

(AHB slave)

1

DNOTITRANS

Code bus mux

HTRANSC