Core Debug

10-6

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

If not enabled for Halting mode,

C_DEBUGEN

= 1, all other fields are disabled.

This register is not reset on a system reset. It is reset by a power-on reset. However, the

C_HALT

bit always clears on a system reset.

To halt on a reset, the following bits must be enabled:

•

bit [0],

VC_CORERESET

, of the Debug Exception and Monitor Control

Register

•

bit [0],

C_DEBUGEN

, of the Debug Halting Control and Status Register.

Note

Writes to this register in any size other than word are Unpredictable. It is acceptable to

read in any size, and you can use it to avoid or intentionally change a sticky bit.

10.2.2

Debug Core Register Selector Register

The purpose of the

Debug Core Register Selector Register

(DCRSR) is to select the

processor register to transfer data to or from.

The DCRSR:

•

is a 17-bit write-only register

•

address is

0xE000EDF4

.

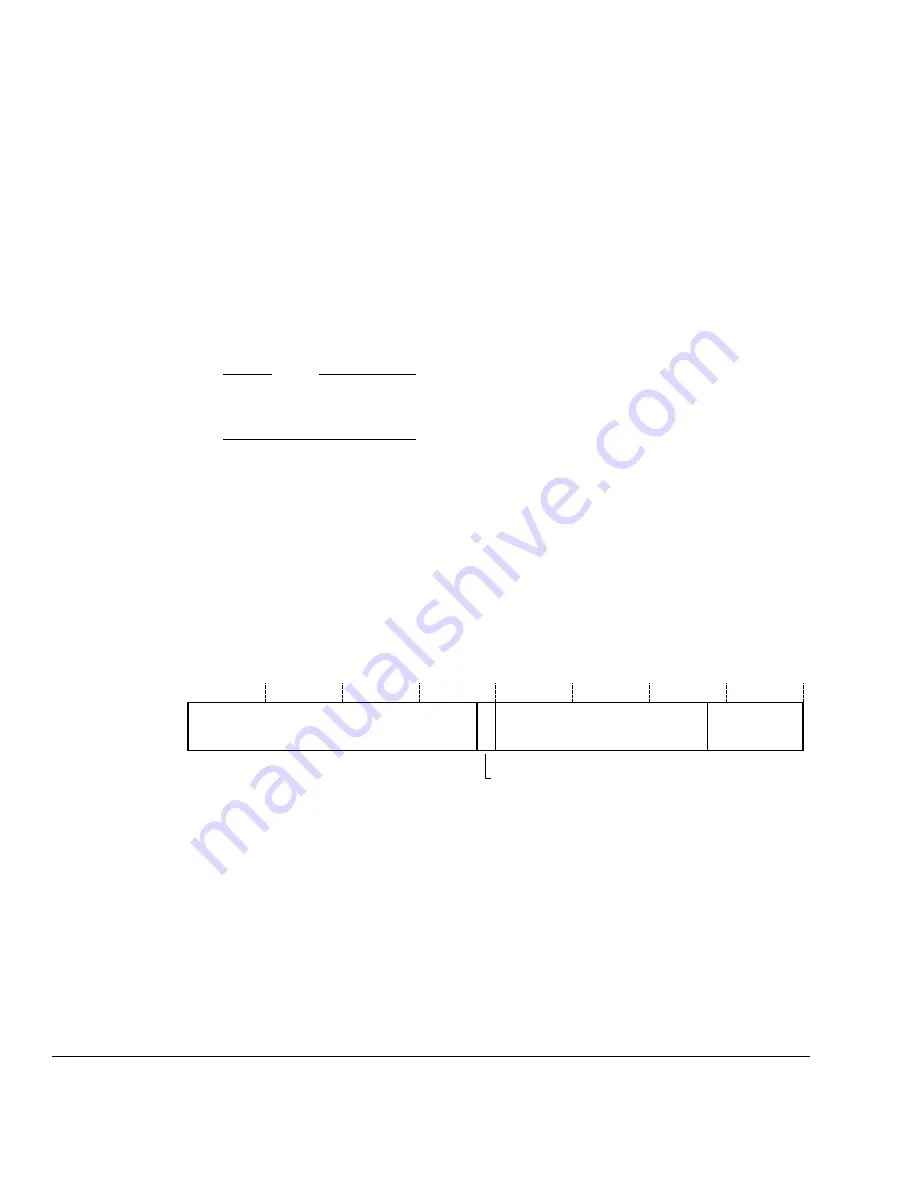

Figure 10-2 shows the bit assignments in the register.

Figure 10-2 Debug Core Register Selector Register bit assignments

REGSEL

Reserved

REGWnR

31

0

15

16

17

Reserved

4

5