Nested Vectored Interrupt Controller

8-20

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

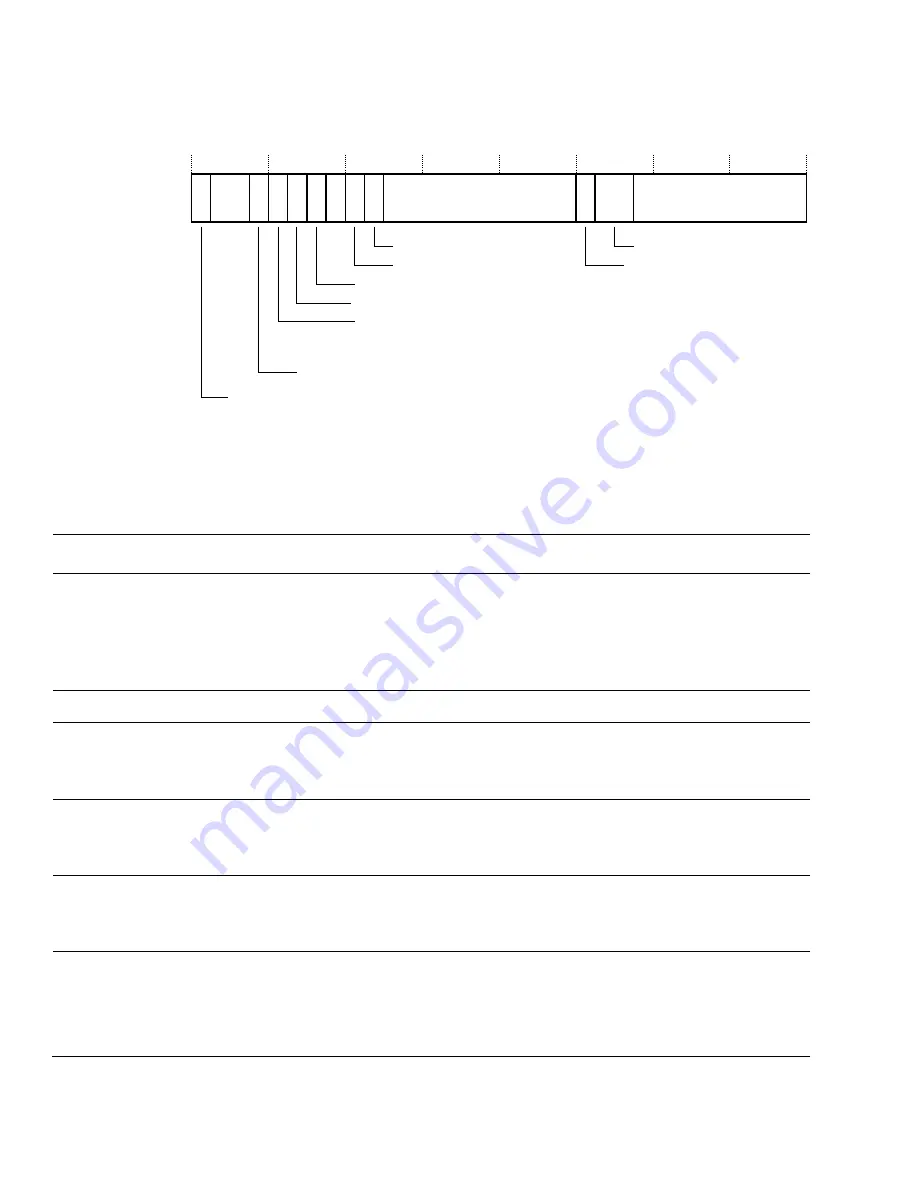

Figure 8-9 Interrupt Control State Register bit assignments

Table 8-15 describes the bit assignments of the Interrupt Control State Register.

31

28

22 21

9

10

0

VECTACTIVE

30 29

27 26

23

24

12 11

VECTPENDING

NMIPENDSET

PENDSVSET

PENDSVCLR

ISRPREEMPT

ISRPENDING

Res.

RESERVED

RETTOBASE

25

PENDSTSET

PENDSTCLR

Res.

8

Table 8-15 Interrupt Control State Register bit assignments

Bits

Field

Type

Function

[31]

NMIPENDSET

Read/write

Set pending NMI bit:

1 = set pending NMI

0 = do not set pending NMI.

NMIPENDSET pends and activates an NMI. Because NMI is the

highest-priority interrupt, it takes effect as soon as it registers.

[30:29]

-

-

Reserved.

[28]

PENDSVSET

Read/write

Set pending pendSV bit:

1 = set pending pendSV

0 = do not set pending pendSV.

[27]

PENDSVCLR

Write-only

Clear pending pendSV bit:

1 = clear pending pendSV

0 = do not clear pending pendSV.

[26]

PENDSTSET

Read/write

Set a pending SysTick bit

1 = set pending SysTick

0 = do not set pending SysTick.

[25]

PENDSTCLR

Write-only

Clear pending SysTick bit:

1 = clear pending SysTick

0 = do not clear pending SysTick.