Nested Vectored Interrupt Controller

8-36

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

The register address, access type, and Reset state are:

Address

0xE000ED2A

Access

Read/write clear

Reset state

0x00000000

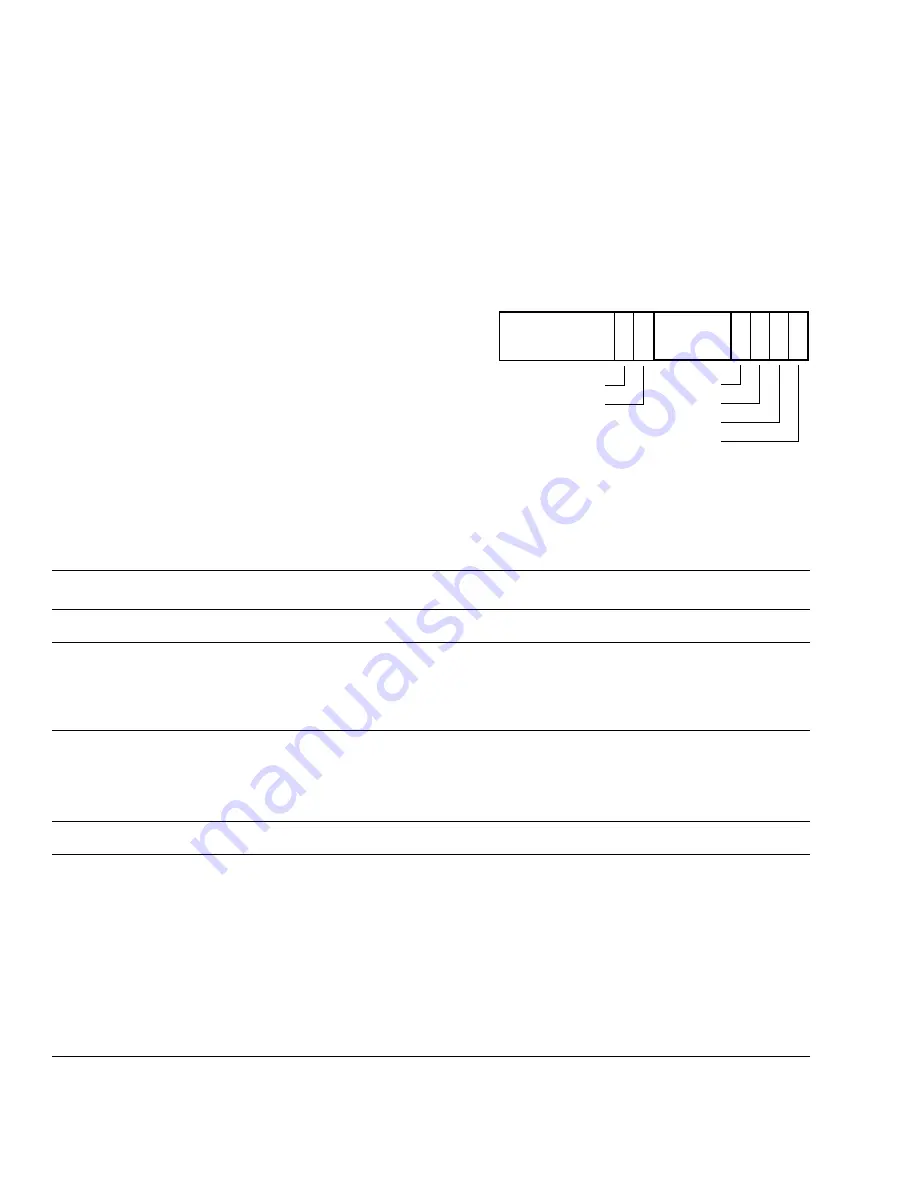

Figure 8-19 shows the bit assignments of the Usage Fault Status Register.

Figure 8-19 Usage Fault Status Register bit assignments

Table 8-24 describes the bit assignments of the Usage Fault Status Register.

7

4 3 2 1 0

NOCP

Reserved

INVPC

INVSTATE

UNDEFINSTR

8

9

DIVBYZERO

UNALIGNED

10

15

Reserved

Table 8-24 Usage Fault Status Register bit assignments

Bits

Field

Function

[15-10]

-

Reserved

[9]

DIVBYZERO

When DIV_0_TRP (see

Configuration Control Register

on page 8-26) is enabled and an

SDIV or UDIV instruction is used with a divisor of 0, this fault occurs The instruction is

executed and the return PC points to it. If DIV_0_TRP is not set, then the divide returns a

quotient of 0.

[8]

UNALIGNED

When UNALIGN_TRP is enabled (see

Configuration Control Register

on page 8-26), and

there is an attempt to make an unaligned memory access, then this fault occurs.

Unaligned LDM/STM/LDRD/STRD instructions always fault irrespective of the setting of

UNALIGN_TRP.

[7:4]

-

Reserved.

[3]

NOCP

Attempt to use a coprocessor instruction. The processor does not support coprocessor

instructions.