Clocking and Resets

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

6-7

Unrestricted Access

Non-Confidential

Note

You must consider LOCKUP from the Cortex-M3 system for inclusion in any external

watchdog circuitry when an external debugger is not attached.

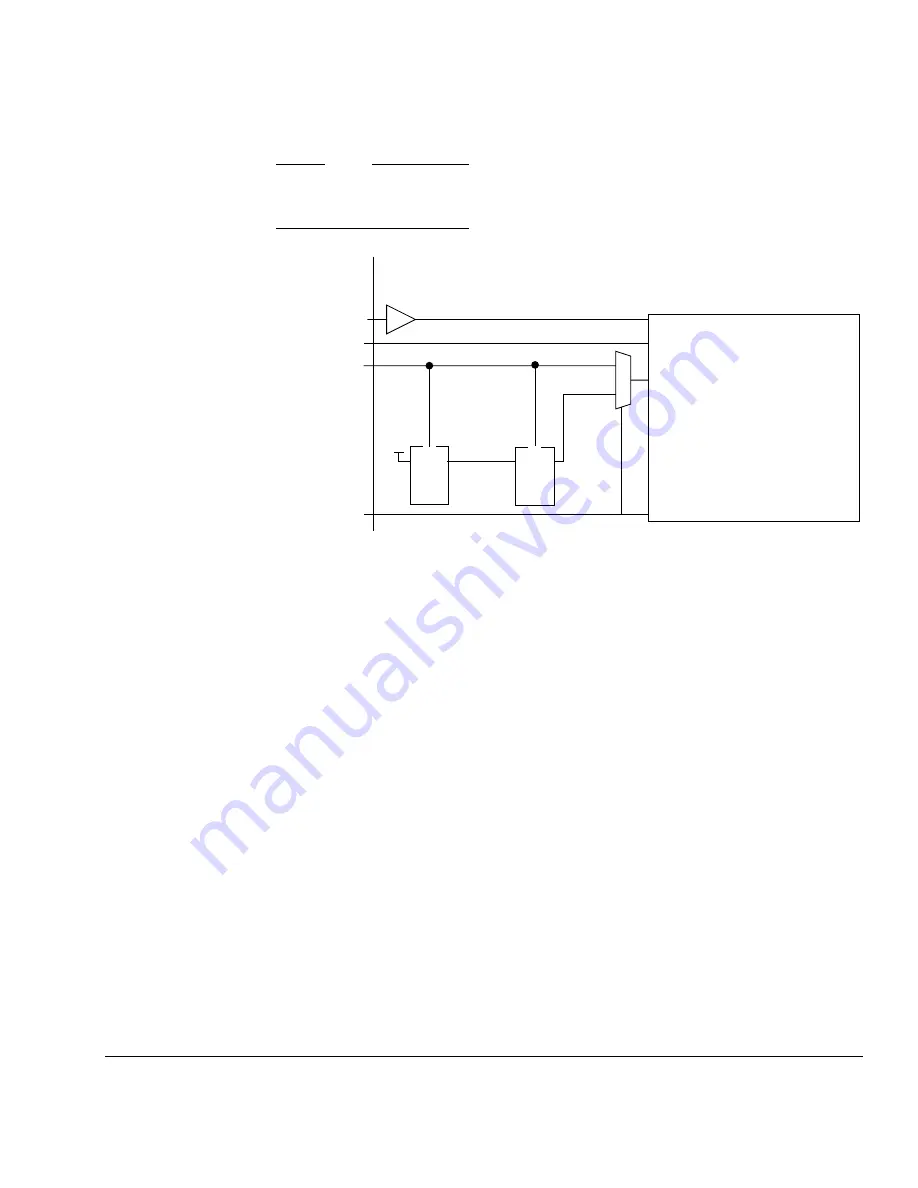

Figure 6-3 Internal reset synchronization

6.3.2

System reset

A system or

warm

reset initializes the majority of the macrocell, excluding the NVIC

debug logic, FPB, DWT, and ITM. System reset typically resets a system that has been

operating for some time, for example, watchdog reset.

SYSRESETn

must be synchronized external to the processor. Figure 6-3 shows the

example reset synchronization provided in CortexM3Integration.

Cortex-M3 exports a signal,

SYSRESETREQ

, that is asserted when the

SYSRESETREQ

bit of the Application Interrupt and Reset Control Register is set. For

example, you can use this as an input to a watchdog timer as Figure 6-1 on page 6-6

shows.

6.3.3

SWJ-DP reset

nTRST

reset initializes the state of the SWJ-DP controller.

nTRST

reset is typically

used by the RealView

™

ICE module for hot-plug connection of a debugger to a system.

nTRST

enables initialization of the SWJ-DP controller without affecting the normal

operation of the processor.

CortexM3

D

Q

CortexM3Integration

SoC

Rn

D

Q

V

dd

HCLK

SE

RSTBYPASS

PORESETn,

SYSRESETn

1

0

Rn