Core Debug

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

10-9

Unrestricted Access

Non-Confidential

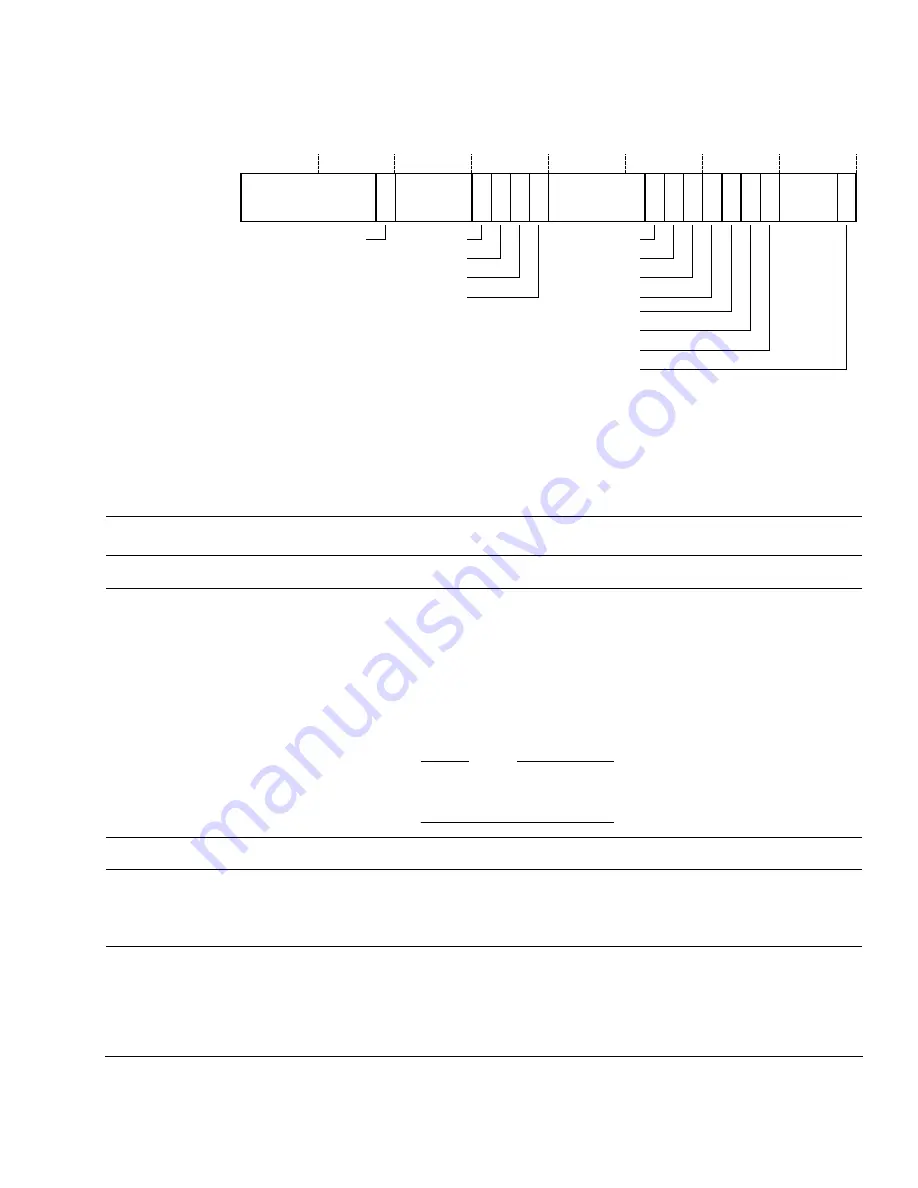

Figure 10-3 Debug Exception and Monitor Control Register bit assignments

Table 10-4 shows the bit functions of the Debug Exception and Monitor Control

Register.

SBZP

SBZP

SBZP

SBZP

31

1

0

TRCENA

3

4

5

6

7

8

9

10

11

15

16

17

18

19

20

23

24

25

MON_REQ

VC_HARDERR

MON_STEP

MON_EN

MON_PEND

VC_INTERR

VC_BUSERR

VC_STATERR

VC_CHKERR

VC_NOCPERR

VC_MMERR

VC_CORERESET

Table 10-4 Debug Exception and Monitor Control Register

Bits

Type

Field

Function

[31:25]

-

-

Reserved, SBZP

[24]

Read/write

TRCENA

This bit must be set to 1 to enable use of the trace and debug blocks:

•

Data Watchpoint and Trace

(DWT)

•

Instrumentation Trace Macrocell

(ITM)

•

Embedded Trace Macrocell

(ETM)

•

Trace Port Interface Unit

(TPIU).

This enables control of power usage unless tracing is required. The

application can enable this, for ITM use, or use by a debugger.

Note

If no debug or trace components are present in the implementation then

it is not possible to set TRCENA.

[23:20]

-

-

Reserved, SBZP

[19]

Read/write

MON_REQ

a

This enables the monitor to identify how it wakes up:

1 = woken up by MON_PEND

0 = woken up by debug exception.

[18]

Read/write

MON_STEP

a

When

MON_EN

= 1, this steps the core. When

MON_EN

= 0, this bit

is ignored. This is the equivalent to

C_STEP

. Interrupts are only

stepped according to the priority of the monitor and settings of

PRIMASK, FAULTMASK, or BASEPRI.