Nested Vectored Interrupt Controller

8-32

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

Configurable Fault Status Registers

Use the three Configurable Fault Status Registers to obtain information about local

faults. These registers include:

•

Memory Manage Fault Status Register

•

Bus Fault Status Register

on page 8-34

•

Usage Fault Status Register

on page 8-35.

The flags in these registers indicate the causes of local faults. Multiple flags can be set

if more than one fault occurs. These register are read/write-clear. This means that they

can be read normally, but writing a 1 to any bit clears that bit.

The register addresses, access types, and Reset states are:

Address

0xE000ED28

Memory Manage Fault Status Register

0xE000ED29

Bus Fault Status Register

0xE000ED2A

Usage Fault Status Register

Access

Read/write-one-to-clear

Reset state

0x00000000

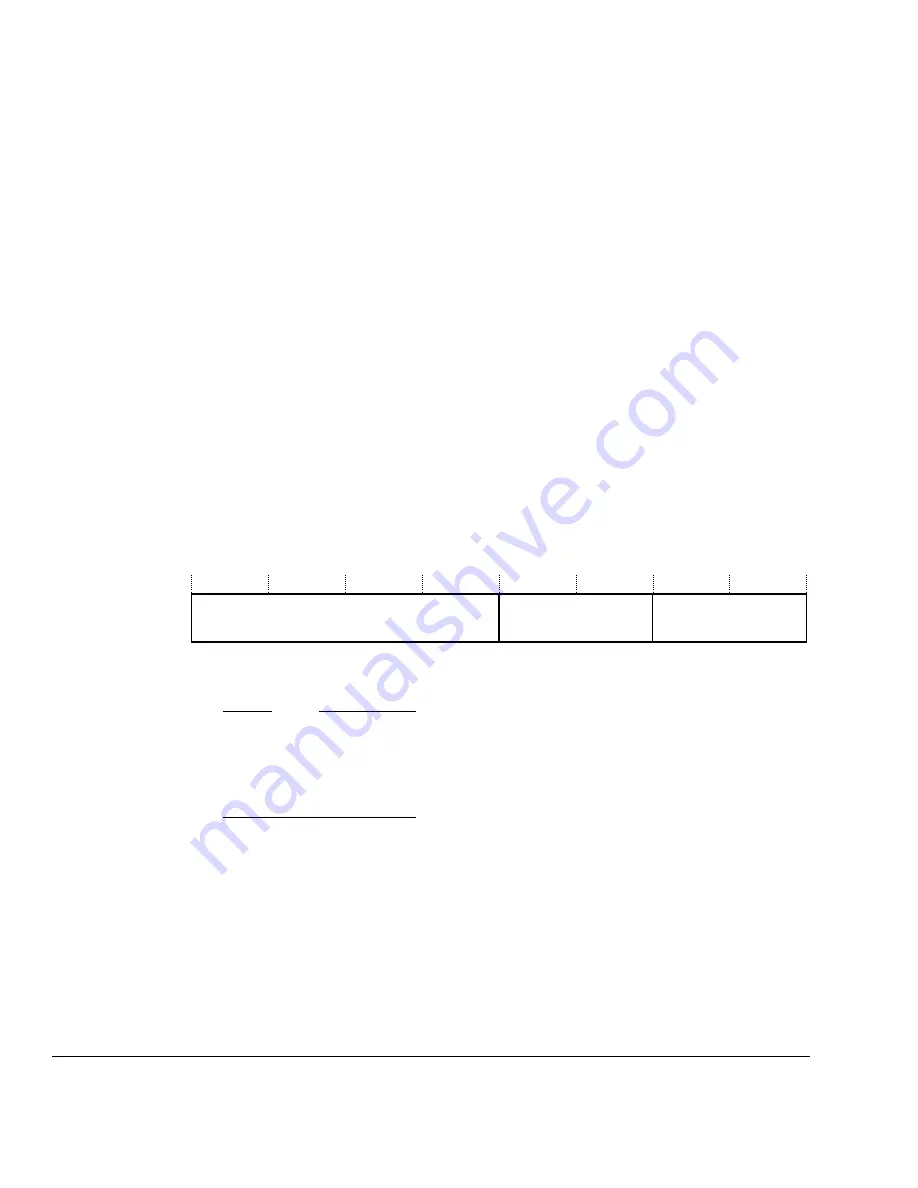

Figure 8-16 shows the bit assignments of the Configurable Fault Status Registers.

Figure 8-16 Configurable Fault Status Registers bit assignments

Note

Accesses to each individual status register must be aligned to the appropriate address

and size. Either the whole 32-bit word is accessed using address

0xE000ED28

or the BFSR

and MFSR are accessed as a byte size each correctly aligned or the UFSR is accessed

as a half-word correctly aligned to address

0xE000ED2A

.

Memory Manage Fault Status Register

The flags in the Memory Manage Fault Status Register indicate the cause of memory

access faults.

The register address, access type, and Reset state are:

Address

0xE000ED28

Access

Read/write-one-to-clear

Reset state

0x00000000

31

16 15

8 7

0

Bus Fault Status

Register

Usage Fault Status

Register

Memory Manage

Fault Status Register