Embedded Trace Macrocell Interface

15-10

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

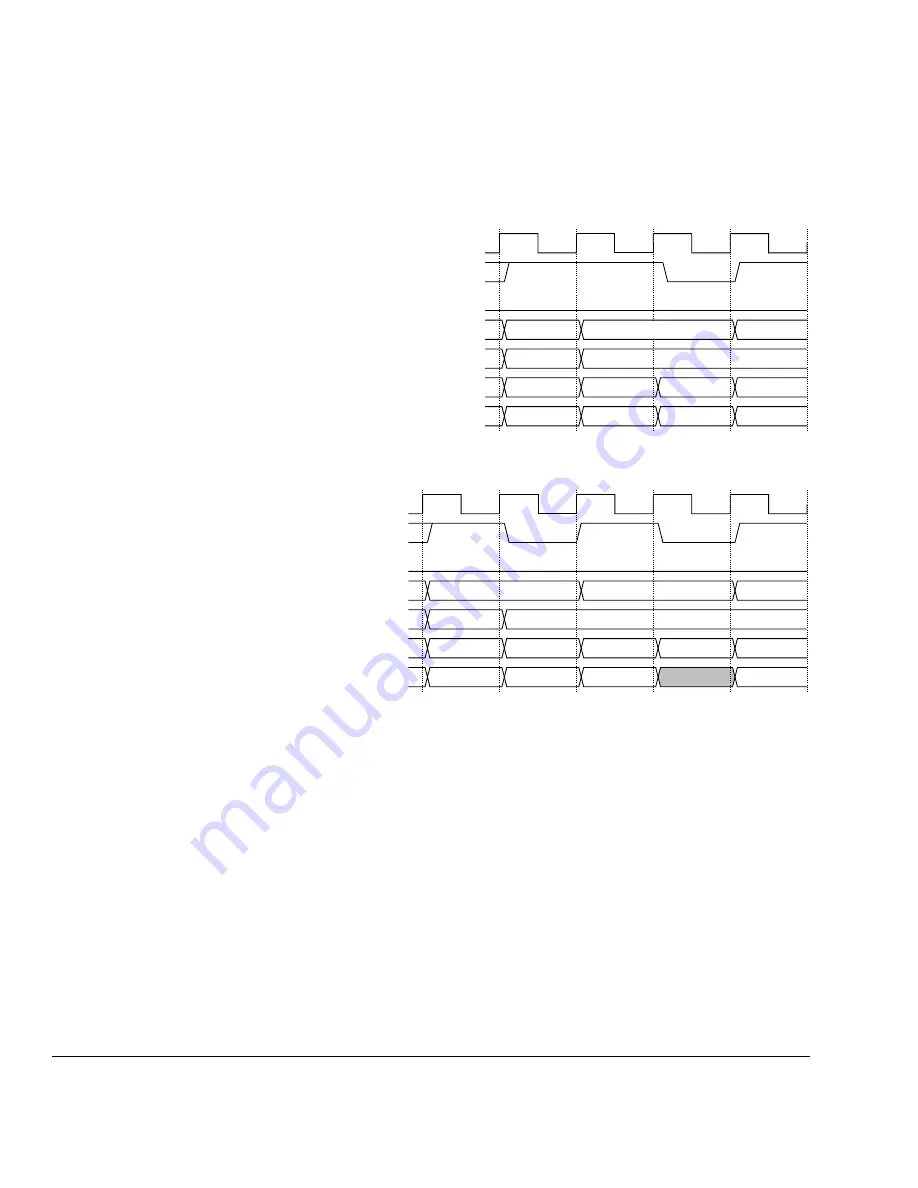

Figure 15-5 and Figure 15-6 show an unconditional branch in this cycle, during the

execute phase of the preceding opcode without and with pipeline stalls. The branch

occurs in the decode phase of the opcode. The branch target is an aligned 32-bit opcode.

Figure 15-5 Unconditional branch without pipeline stalls

Figure 15-6 Unconditional branch with pipeline stalls

Figure 15-7 on page 15-11 and Figure 15-8 on page 15-11 show an unconditional

branch in the next opcode. The branch occurs in the execute phase of the opcode. The

branch target is an aligned and unaligned 32-bit ALU opcode.

ETMIVALID

ETMCCFAIL

ETMIA

BRCHSTAT

HTRANSI

HADDRI

HCLK

0x1000

0x1020

0100

0000

NONSEQ

0x1020

0x1002

NONSEQ

NONSEQ

NONSEQ

0x1024

0x1028

0x102C

0x1002

ETMIVALID

ETMCCFAIL

ETMIA

BRCHSTAT

HTRANSI

HADDRI

HCLK

0x1000

0100

0000

NONSEQ

0x1020

0x1020

NONSEQ

NONSEQ

IDLE

NONSEQ

0x1024

0x1028

0x102C