Chapter 4

General-Purpose Counter/Timer

DAQ-STC Technical Reference Manual

4-2

©

National Instruments Corporation

•

Programmable input and output signal polarities

•

One-shot, continuous, or tri-state output

•

Two banks of dual-load registers that allow seamless frequency and duty cycle changes

during double-buffered pulse-train generation

•

A counter load register that can increment or decrement on TC, which allows for

equivalent time sampling (ETS) timing output. ETS is a sampling method for repetitive

waveforms where the sample point is moved within the cycle. Refer to section

, for more information.

•

Interevent (relative) time stamping

•

Two sets of save registers to save the counter value via an external control signal or via

software command

–

Current count value can be read without affecting circuit operation

•

Bus interface support

–

Interrupts based on TC or on active gate edge—rising edge, falling edge, or any edge

–

Secondary interrupts to facilitate a DMA or local CPU interface for timing functions

•

Not supported in hardware are BCD counting and time-of-day counting

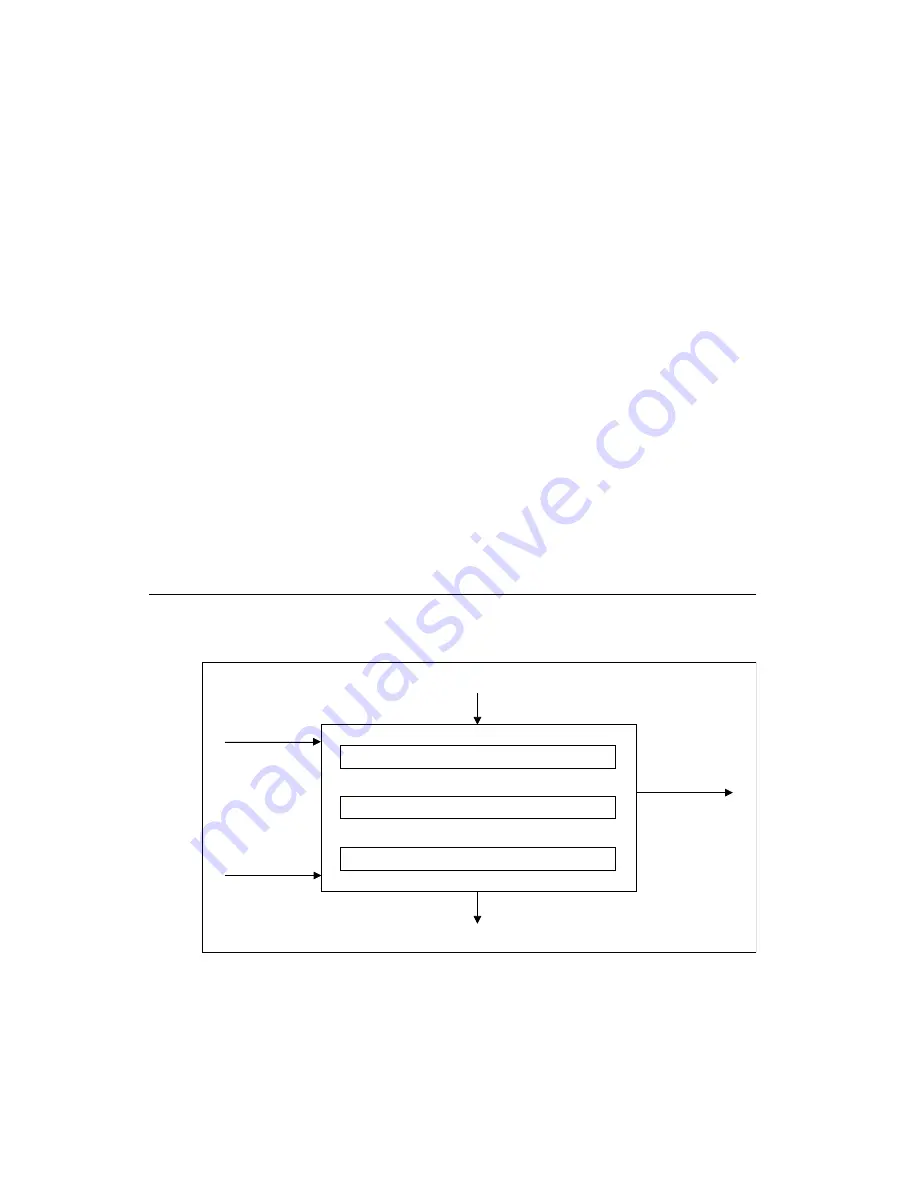

4.3 Simplified Model

The GPCT module contains two identical 24-bit binary up/down counters—general-purpose

counters 0 and 1. Figure 4-1 shows a simplified model of the counter.

Figure 4-1.

General-Purpose Counter/Timer Simplified Model

G_UP_DOWN

G_SOURCE

G_GATE

INTERRUPT

G_OUT

Load Registers

24 Bit Up/Down Counter

Save Registers