Chapter 4

General-Purpose Counter/Timer

©

National Instruments Corporation

4-73

DAQ-STC Technical Reference Manual

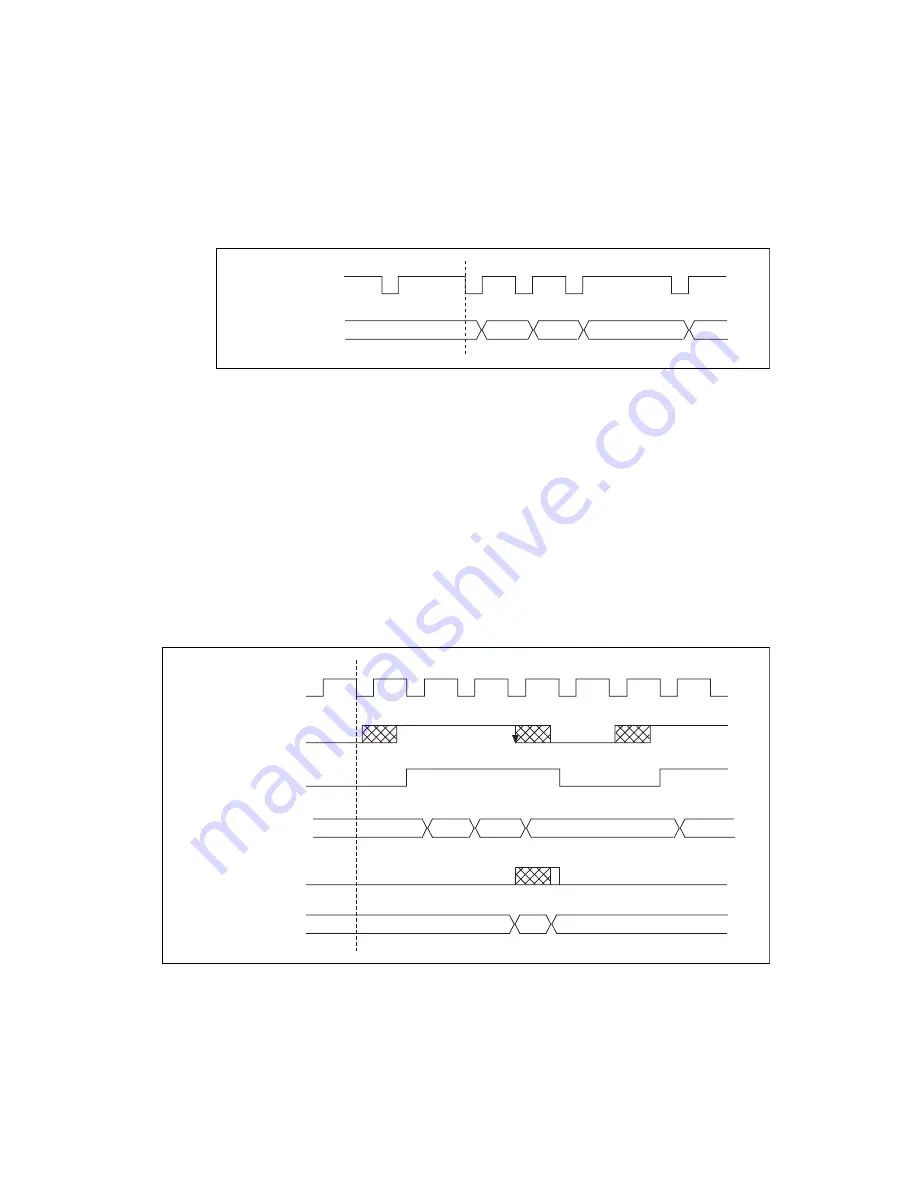

Figure 4-32 shows an example of simple event counting where the counter counts four events

on G_SOURCE. The dotted line indicates where the ARM occurs.

Figure 4-32.

Simple Event Counting

4.8.11.2 Simple Gated-Event Counting

To use this function, set G_CONTROL conditioning to level gating and program the counter

to count on G_CONTROL. G_GATE is synchronized by the falling edge of G_SOURCE to

generate G_CONTROL. The counter increments only when G_CONTROL is high. The HW

save register switches to transparent mode on the falling edge of G_GATE and returns to

latched mode on the next G_SOURCE falling edge.

Figure 4-33 shows an example of simple gated-event counting where the gate action allows

the counter to count only four of the rising edges of G_SOURCE. The HW save register

latches the counter value each time the counting stops. The dotted line indicates where the

ARM occurs and the arrow indicates where the gate interrupt is generated.

Figure 4-33.

Simple Gated-Event Counting

Counter Value

G_SOURCE

0

1

2

3

4

Counter Value

G_SOURCE

G_GATE

G_CONTROL

HW Save

HW Save Register

0

1

2

3

4

3