Chapter 2

Analog Input Timing/Control

©

National Instruments Corporation

2-117

DAQ-STC Technical Reference Manual

SI2_LOAD_SRC

SI2 Load Source—This signal determines which load register, A or B,

the SI2 counter will use on the next reload. The initial SI2 load source is

set using AI_SI2_Initial_Load_Source. The SI2 control logic updates

the load source while the DAQ-STC is counting. The current load source

depends on the counter state and the selected reload mode. Related

bitfields: AI_SI2_Initial_Load_Source.

SI2_SRC

SI2 Source—This signal is the timebase for the SI2 counter. It is equal

to either SI_SRC or AI_IN_TIMEBASE1. Related bitfields:

AI_SI2_Source_Select.

SI2_TC

SI2 TC—This signal is the SCLK signal when internal CONVERT is

selected.

SI_CE

SI Count Enable—This signal enables and disables the SI counter. Refer

to section

, for the SI_CE logic equations.

SI_CLK

SI Clock—This is the actual clock for the SI counter and the SI control

logic. When the counter is not armed, SI_CLK is derived from the write

strobe for AI_Command_1_Register, so that the counter can be loaded

using the load command. When the counter is armed, SI_CLK is the

same as SI_SRC. Related bitfields: AI_SI_Load.

SI_HOLD

SI Hold—This signal controls the SI save register. If SI_HOLD = 0, then

the SI save register tracks the SI counter output. If SI_HOLD = 1, then

the SI save register latches the SI counter output on the next SI_CLK.

SI_LOAD

SI Load—This signal pulses to load the value from the selected SI load

register into the SI counter. Related bitfields: AI_SI_Load.

SI_LOAD_SRC

SI Load Source—This signal determines which load register, A or B, the

SI counter will use on the next reload. The initial SI load source is set

using AI_SI_Initial_Load_Source. The SI control logic updates the load

source while the DAQ-STC is counting. The current load source

depends on the counter state and the selected reload mode. Related

bitfields: AI_SI_Initial_Load_Source.

SI_SRC

SI Source—This signal is the timebase for the SI counter. Related

bitfields: AI_SI_Source_Select.

SI_START1

START1 Synchronized to SI_SRC—This signal is generated by the

hardware by passing the output of the AI_START1 selector through

polarity selection, edge detection, and synchronization (synchronized to

the falling edge of SI_SRC).

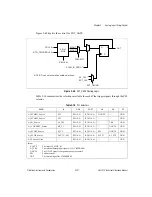

Table 2-9.

Internal Signals (Continued)

Signal

Description