Remote Operation

5-55

5.11.8 Status Byte Register

The Status Byte register summarizes all of the status events from all status registers.

Table 5-8 describes the status events that are applied to the electronic load.

The Status Byte register can be read with a serial poll or *STB? query. The RQS bit is

the only bit that is automatically cleared after a serial poll.

When the Status Byte register is read with a *STB? query, bit 6 of the Status Byte

register will contain the MSS bit. The MSS bit indicates that the load has at least one

reason for requesting service. *STB? does not affect the status byte.

The Status Byte register is cleared by *CLS command.

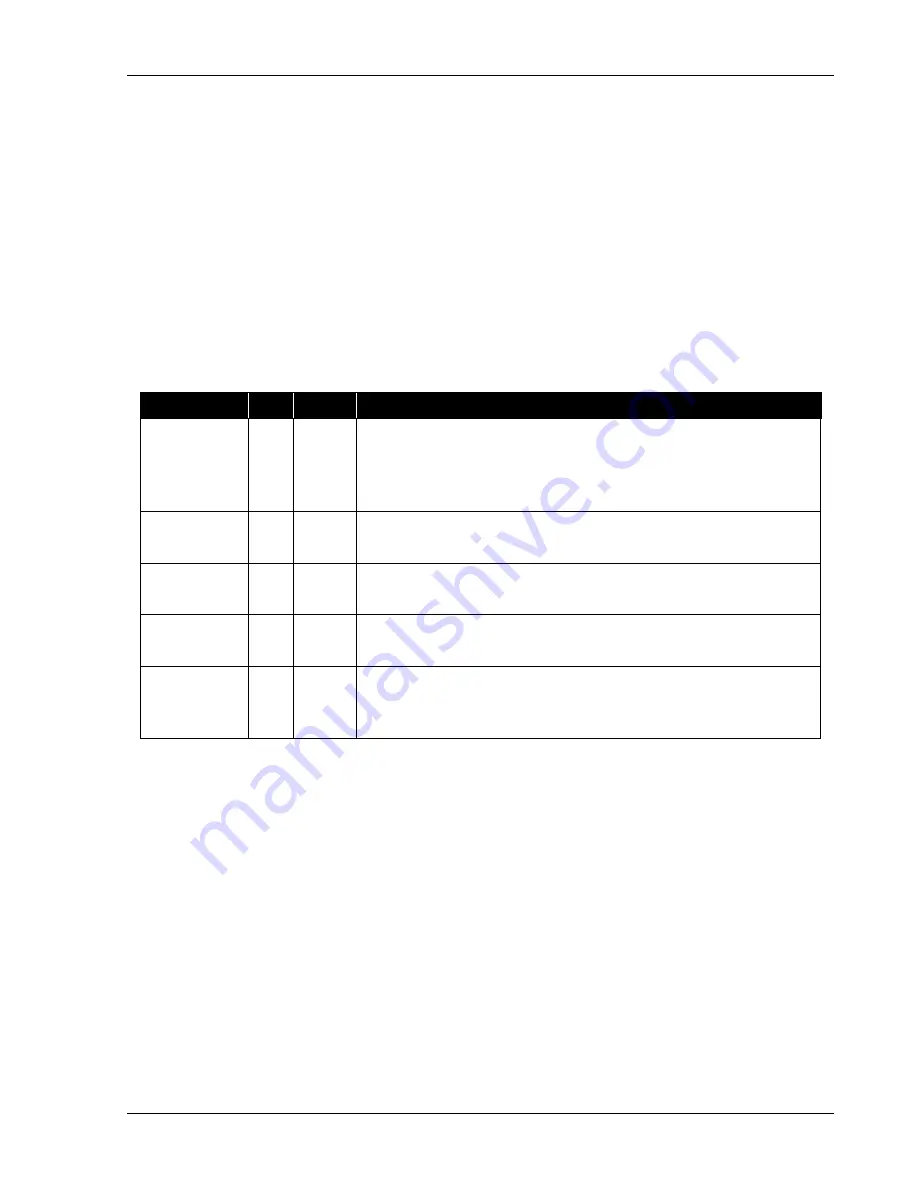

Mnemonic Bit Value

Meaning

CSUM

2

4

Channel Summary

. Indicates if an enabled channel

event has occurred. It is affected by Channel

Condition, Channel Event and Channel Summary

Event registers.

QUES

3 8

Questionable

. Indicates if an enabled questionable

event has occurred.

MAV

4 16

Message Available.

Indicates if the Output Queue

contains data.

ESB

5 32

Event Status Bit

. Indicates if an enabled standard

event has occurred.

RQS/MSS

6 64

Request Service/Master Summary Status.

During a

serial poll, RQS is returned and cleared. For an *STB?

query, MSS is returned without being cleared.

Table 5-8 Bit Description of Status Byte

5.11.9 Service Request Enable Register

The Service Request Enable register can be programmed to specify which bit in the

Status Byte register will generate service requests.

Artisan Scientific - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisan-scientific.com

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com