Chapter 8 DMA Controller

8-8

When the Chain End bit (CHDN) is cleared, the DMADONE* signal is asserted when the

DMAACK[n] signal for the last data transfer in a DMA transfer specified by the current DMA

Channel Register is asserted. Namely, if the Link List Command chain is used, there is one

assertion at the end of each data transfer specified by each Descriptor.

If the DMADONE* signal is set to be used as an input signal (DMCCRn.DNCTRL = 01/11),

DMA transfer can be set to end normally when the external device asserts the DMADONE* signal

when the DMAACK[n] signal of channel

n

is asserted. DMADONE* is asserted during

DMAACK[n] is not asserted, then unexpected operation occurs. When DMA transfer is

terminated by the DMADONE* assertion of the external device, the External DONE Assert bit

(DMCSRn.EXTDN) of the DMA Channel Status Register is set regardless of the setting of the

Chain End bit (CHDN) of the DMA Channel Control Register (DMCCRn). Operation is as

follows depending on the setting of the Chain End bit (CHDN).

When the Chain End bit (CHDN) is set, all DMA transfer for that chain is terminated. At this

time, the Normal Chain End bit (NCHNC) and the Normal Transfer End bit (NTRNFC) of the

DMA Channel Status Register are both set and the Transfer Active bit (DMCCRn.XFACT) of the

DMA Channel Control Register is cleared.

When the Chain End bit (CHDN) is cleared, only DMA transfer specified by the current DMA

Channel Register ends normally, and only the Normal Transfer End bit (NTRNFC) is set. When

the Chain Enable bit (CHNEN) of the DMA Channel Control Register (DMCCRn) is set, chain

transfer is executed and DMA transfer continues. When the Chain Enable bit (CHNEN) is cleared,

the Transfer Active bit (DMCCRn.XFACT) is cleared and the Normal Chain End bit (NCHNC) is

set.

Three clock cycles are required from external assertion of the DMADONE* signal to disabling

of new DMA access. Operation will not stop even if the bus operation in progress is a Single

transfer or a Burst transfer. For example, if the DMADONE* signal is asserted during Read

operation of Dual Address transfer, the corresponding Write bus operation will also be executed.

If the DMADONE* pin is set to become both input and output for channel

n

(DMCCRn.DNCTRL = “11”), the DMADONE* signal becomes an open drain signal when the

channel becomes active. When used by this mode, the DMADONE* signal must be pulled up by

an external source. When in this mode, the External DONE Assert bit (DMCSRn.EXTDN) is not

only set when asserted by an external device, but is also set when asserted by the TX4937.

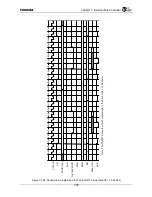

8.3.4

Internal I/O DMA Transfer Mode

Performs DMA with the on-chip Serial I/O Controller and the AC-link Controller. Set the DMA

Channel Control Register (DMCCRn) as follows.

•

DMCCRn.EXTRQ

=

1: I/O DMA Transfer mode

•

DMCCRn.SNGAD

=

0: Dual Address Transfer

Refer to “8.3.8 Dual Address Transfer” and “11.3.6 DMA transfer (Serial I/O Controller)” or

“14.3.6.4 DMA operation (AC-link Controller) for more information.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...