Chapter 20 Extended EJTAG Interface

20-3

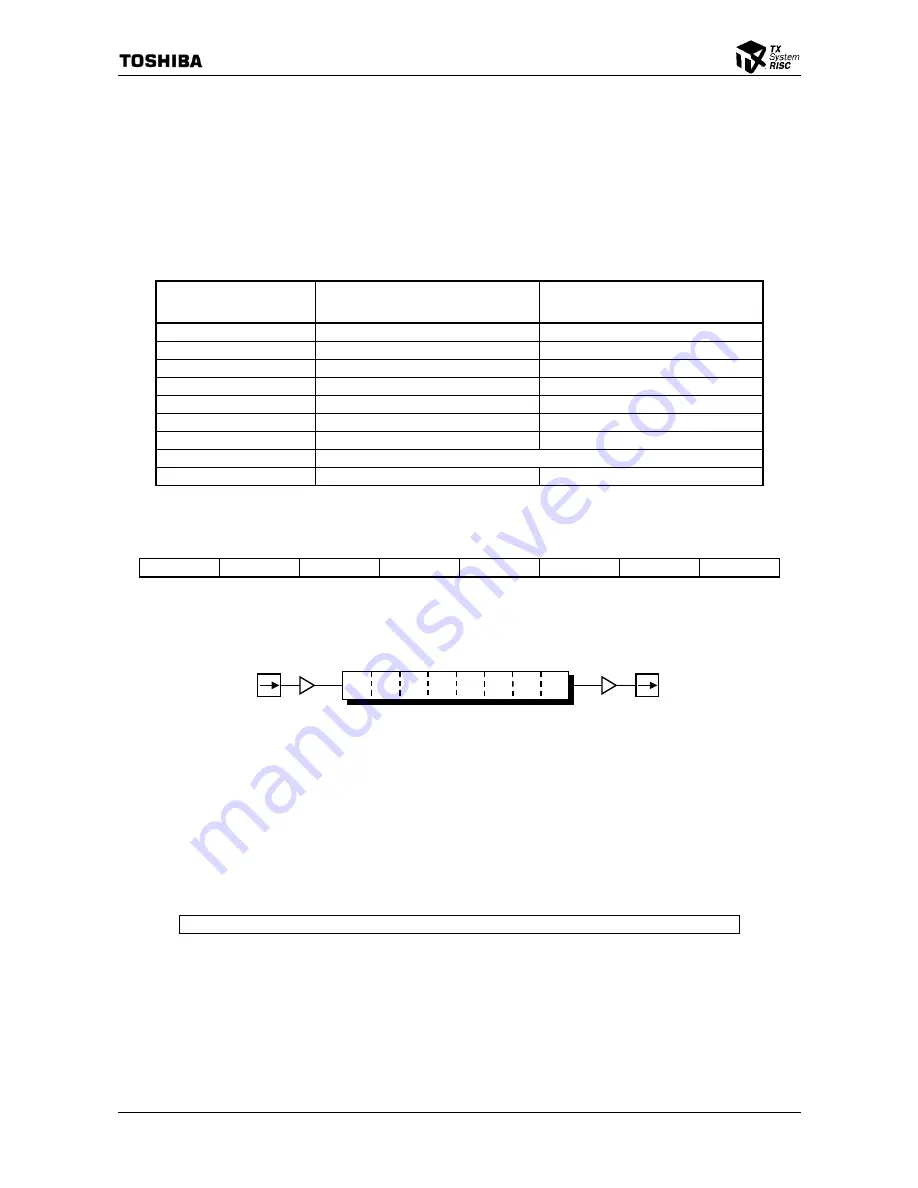

20.2.2 Instruction

Register

The JTAG Instruction Register consists of an 8-bit shift register. This register is used for selecting

either one or both of the test to be performed and the Test Data Register to be accessed. The Data

Register is selected according to the instruction code in Table 20.2.1. Refer to the “64-bit TX System

RISC TX49/H2, TX49/H3, TX49/H4 Core Architecture” for more information regarding each

instruction.

Table 20.2.1 Bit Configuration of JTAG Instruction Register

Instruction Code

MSB

→

LSB

Instruction

Selected Data Register

00000000 (0x00)

EXTEST

Boundary Scan Register

00000001 (0x01)

SAMPLE/PRELOAD

Boundary Scan Register

00000010 (0x02)

Reserved

Reserved

00000011 (0x03)

IDCODE

Device ID Register

00000100 - 00001111

Reserved

Reserved

00010000 (0x10)

HIGHZ

Bypass Register

00010001 - 01111111

Reserved

Reserved

10000000 - 11111110

Refer to the “64-bit TX System RISC TX49/H2, TX49/H3, TX49/H4 Core Architecture”

11111111 (0xFF)

BYPASS

Bypass Register

Figure 20.2.1 shows the format of the Instruction Register.

7 6 5 4 3 2 1 0

MSB

LSB

Figure 20.2.1 Instruction Register

The instruction code is shifted to the Instruction Register starting from the Least Significant Bit.

LSB

TDO

TDI

MSB

Figure 20.2.2 Shift Direction of the Instruction Register

20.2.3 Boundary Scan Register

The Boundary Scan Register contains a single 391-bit shift register to which all TX4937 I/O signals

except for power supply, TDI, TCK, TDO, TMS, TRST*, and TEST[4]* are connected. Figure 20.2.3 shows

the bits of the Boundary Scan Register.

390 0

Refer to TX4937 BSDL file

Figure 20.2.3 Boundary Scan Register

TDI input is fetched to the Most Significant Bit (MSB) of the Boundary Scan Register and the Least

Significant Bit (LSB) of the Boundary Scan Register is sent from the TDO output.

Table 20.2.2 shows the boundary scan sequence relative to the processor signals.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...