Chapter 3 Signals

3-5

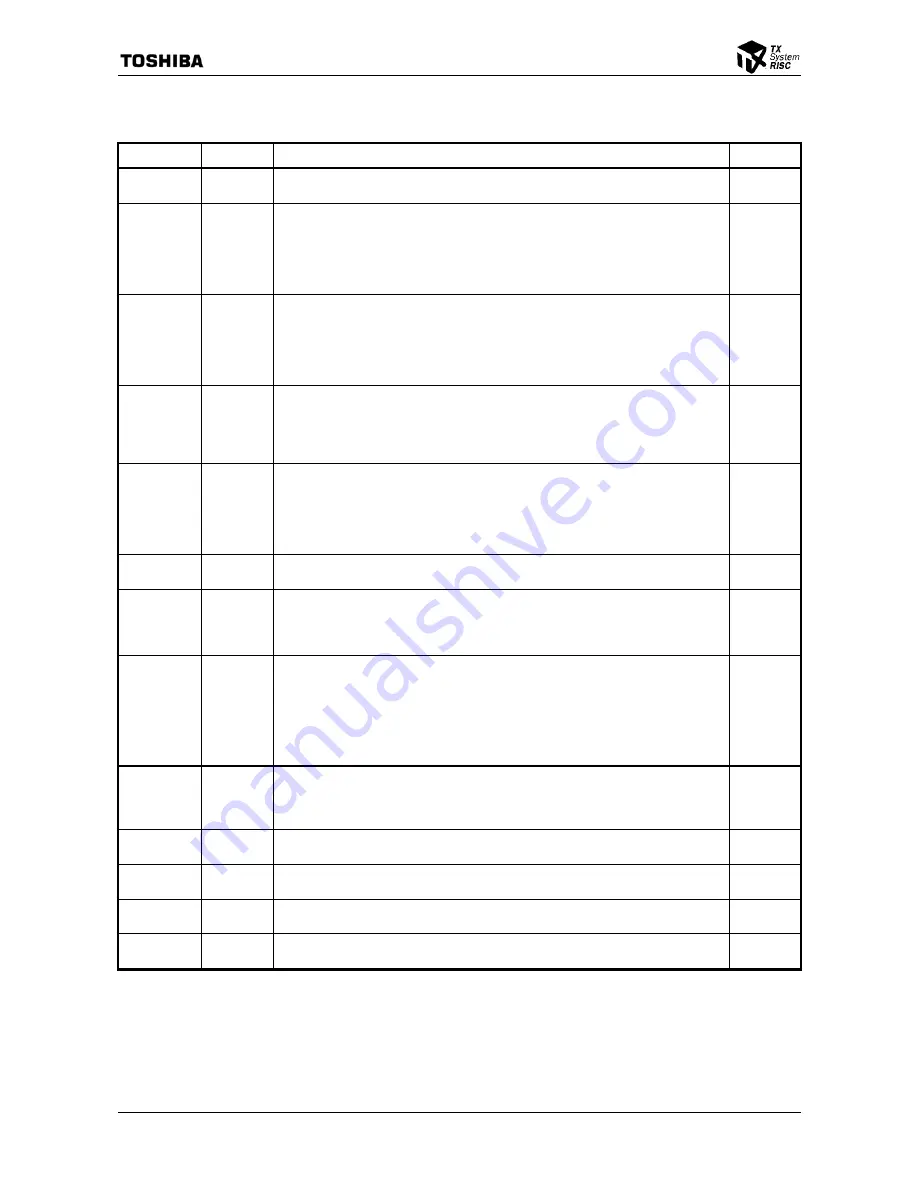

Table 3.1.5 PCI Interface Signals (2/2)

Signal Name

Type

Description

Initial State

DEVSEL

*

Input/output Device Select

The target asserts this signal in response to access from the initiator.

Input

REQ[3:2]

*

Input

Request

Signals used by the master to request bus mastership. The boot configuration signal on

the DATA[2] pin determines whether the built-in PCI bus arbiter is used. In internal arbiter

mode, REQ[3:2]

*

are PCI bus request input signals. In external arbiter mode, REQ[3:2]

*

are not used. Because the pins are still placed in the input state, they must be pulled up

externally.

Input

REQ[1]

*

/INTOUT

Input/output/

OD

Request

Signal used by the master to request bus mastership. The boot configuration signal on

the DATA[2] pin determines whether the built-in PCI bus arbiter is used. In internal arbiter

mode, this signal is a PCI bus request input signal. In external arbiter mode, this signal is

an external interrupt output signal (INTOUT). Refer to Section “15.3.7 Interrupt

Requests”.

Selected by

DATA[2]

H: Input

L: Hi-Z

REQ[0]

*

Input/output

Request

Signal used by the master to request bus mastership. The boot configuration signal on

the DATA[2] pin determines whether the built-in PCI bus arbiter is used. In internal arbiter

mode, this signal is a PCI bus request input signal. In external arbiter mode, this signal is

a PCI bus request output signal.

Selected by

DATA[2]

H: Input

L: High

GNT[3:0]

*

Input/output

Grant

Indicates that bus mastership has been granted to the PCI bus master. The boot

configuration signal on the DATA[2] pin determines whether the built-in PCI bus arbiter is

used. In internal arbiter mode, all of GNT[3:0]

*

are PCI bus grant output signals. In

external arbiter mode, GNT[0]

*

is a PCI bus grant input signal. Because GNT[3:1]

*

also

become input signals, they must be pulled up externally.

Selected by

DATA[2]

H: All High

L: Input

PERR

*

Input/output

Data

Parity

Error

Indicates a data parity error in a bus cycle other than special cycles.

Input

SERR

*

Input/OD

System

Error

Indicates an address parity error, a data parity error in a special cycle, or a fatal error.

In host mode, SERR

*

is an input signal. In satellite mode, SERR

*

is an open-drain output

signal. The mode is determined by the boot configuration signal on the ADDR[19] pin.

Input

M66EN

Input/output PCI Bus 66 MHz Clock Enable

1: Enable 66 MHz operating mode.

0: Disable 66 MHz operating mode.

This pin is configured as input in satellite mode and as output in host mode. The mode is

selected through the logic level of the ADDR[19] pin at boot time. This pin must be pulled

down when the PCI Controller is configured in satellite mode and when the 66-MHz

operating mode is disabled.

Selected by

ADDR[19]

H: Low

L: Input

PME

*

Input/OD

Power Management Event

PME

*

indicates the power management mode. In host mode, PME

*

is an input signal. In

satellite mode, PME

*

is an open-drain output signal. The mode is determined by the boot

configuration signal on the ADDR[19] pin.

Selected by

ADDR[19]

H: Input

L: Hi-Z

EEPROM_DI Input

PU

EEPROM Data In

Data input from serial EEPROM for initially setting the PCI configuration.

Input

EEPROM_DO Output EEPROM

Data

Out

Data output to serial EEPROM for initially setting the PCI configuration.

Low

EEPROM_CS Output EEPROM

Chip

Select

Chip select for serial EEPROM for initially setting the PCI configuration.

Low

EEPROM_SK Output EEPROM

Serial

Clock

Clock for serial EEPROM for initially setting the PCI configuration.

Low

Note: The PCI bus specification specifies that the following pins require pullups: FRAME

*

, IRDY

*

,

TRDY

*

, STOP

*

, LOCK

*

, DEVSEL

*

, PERR

*

, SERR

*

and PME

*

. If these pins are unused, pullups

must be provided externally to the TX4937.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...