Chapter 10 PCI Controller

10-44

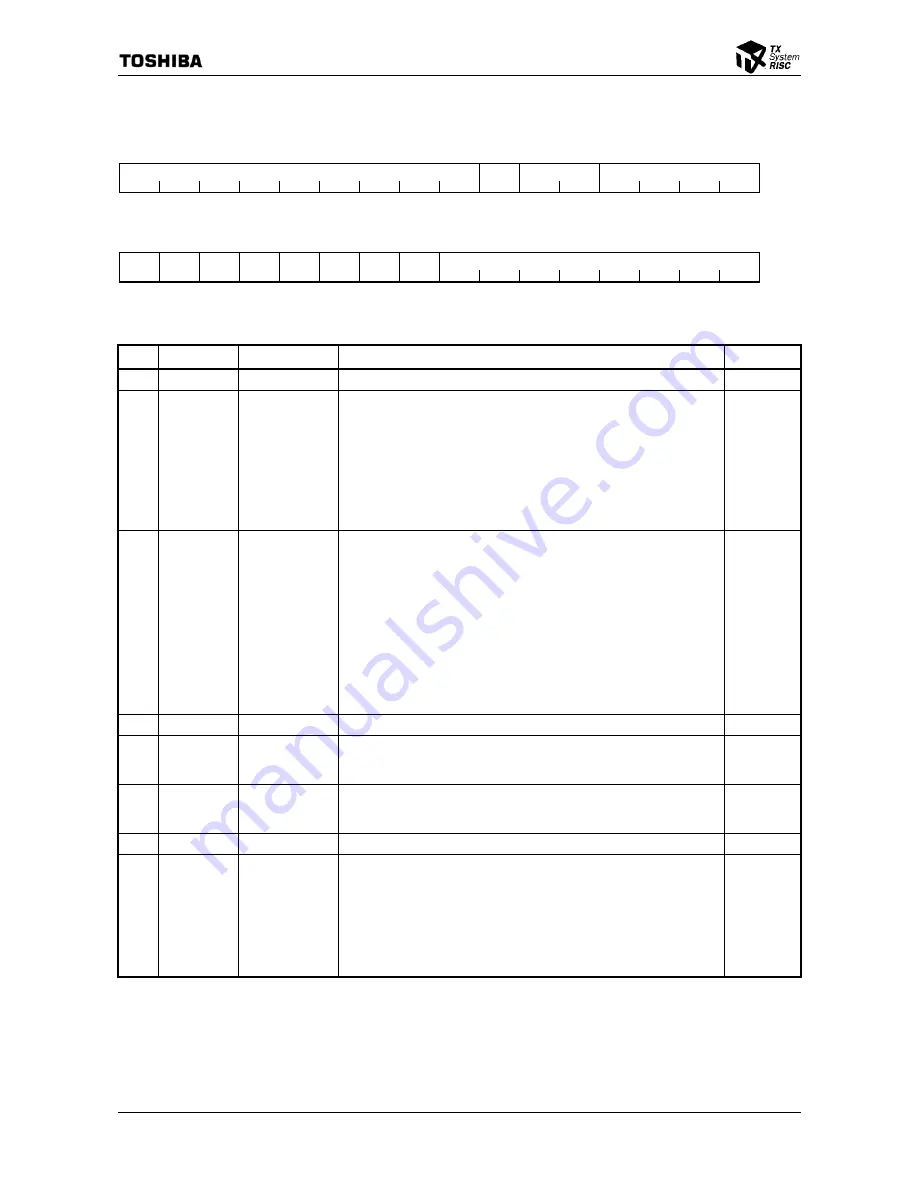

10.4.19 P2G Configuration Register (P2GCFG)

0xD090

31 23

22

21

20

19 16

Reserved PME

TPRBL

Reserved

R/W1S

R/W

: Type

0x0 0x3

:

Initial

value

15

14

13

12

11

10

9 8

7 0

FTRD FTA

Reserved

MEM0PD MEM1PD MEM2PD

TOBFR TIBFR

Reserved

R/W R/W R/W R/W R/W R/W R/W

:

Type

0x0 0x0 0x0 0x0 0x1 0x0 0x0

:

Initial

value

Bit Mnemonic Field

Name

Description

Read/Write

31:23

Reserved

⎯

22

PME

PME

PME (Default: 0x0)

When the PCI Controller is in the Satellite mode, writing “1” to this bit

signals a PME (Power Management Event) to the PCI Host device. The

PME

*

signal is asserted if the PME_Status bit of the PMCSR Register is

set and the PME_En bit of the PMCSR Register is set.

This bit is cleared when the PCI Host device writes a “1” to the PME_Status

bit of the PMCSR Register.

This bit is invalid when the PCI Contoller is in the Host mode since the

PME

*

signal is an input signal.

R/W1S

21:20 TPRBL Target Prefetch

Read Burst

Length

Target Prefetch Read Burst Length (Default: 0x3)

These bits set the number of DWORDS (32-bit words) to be read into the

data FIFO when prefetching is valid during a target memory Read

operation.

Extra data transferred to the data FIFO is deleted when performing a

memory Read operation of a PCI Bus transfer that is smaller than the set

size.

This setting is invalid when prefetching is disabled.

0x00: Access and transfer each 2 DWORDs of data to the target read FIFO.

0x01: Access and transfer each 4 DWORDs of data to the target read FIFO.

0x10: Access and transfer each 6 DWORDs of data to the target read FIFO.

0x11: Access and transfer each 8 DWORDs of data to the target read FIFO.

R/W

19:16

Reserved

⎯

15 FTRD

Force Target

Retry/Disconnect

Force Target Retry/Disconnect (Default: 0x0)

The PCI Controller executes Retry Termination on a PCI Read access

transaction if this bit is set to “1”. This is a diagnostic function.

R/W

14 FTA

Force Target

Abort

Force Target Abort (Default: 0x0)

The PCI Controller executes a Target Abort on a PCI Read access

transaction if this bit is set to “1”. This is a diagnostic function.

R/W

13

Reserved

⎯

12 MEM0PD

Memory 0

Window Prefetch

Disable

Memory 0 Window Prefetch Disable (Default: 0x0)

Prefetching during a G-Bus Burst Read transfer cycle to the Memory 0

Space is disabled when this bit is set to “1”. PCI Burst Read transactions

are not supported when prefetching is disabled.

Even if the setting of this bit is changed, prefetchable bits in the Base

Address Register of the PCI Configuration Space will not reflect this

change. We recommend using the default setting when the PCI Controller

is in the Satellite mode.

R/W

Figure 10.4.17 P2G Configuration Register (1/2)

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...