ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 105 -

Revision 2.4

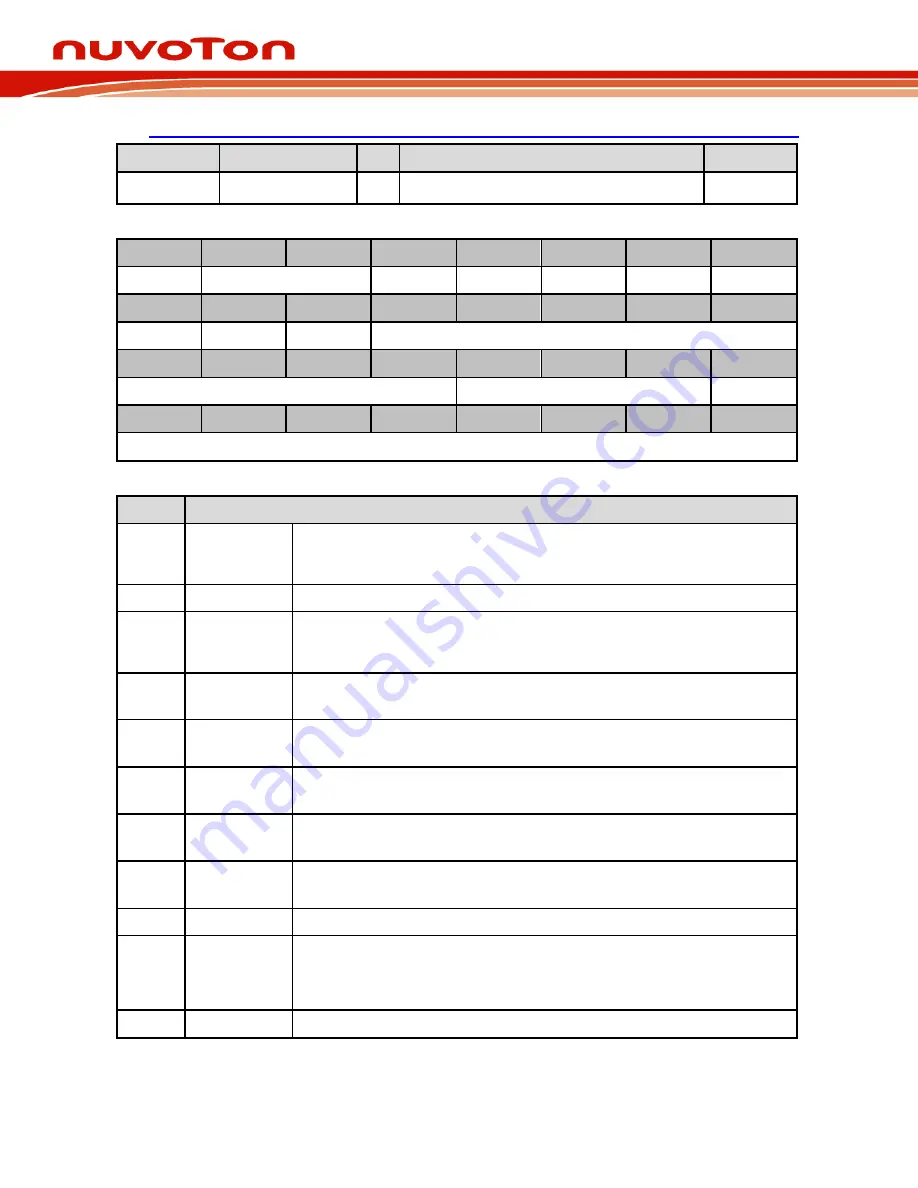

Interrupt Control State Register (SYSINFO_ICSR)

Register

Offset

R/W

Description

Reset Value

SYSINFO_ICSR

SYS0x004

R/W

Interrupt Control State Register

0x0000_0000

31

30

29

28

27

26

25

24

NMIPNSET

Reserved

PPSVISET

PPSVICLR

PSTKISET

PSTKICLR

Reserved

23

22

21

20

19

18

17

16

ISRPREEM

ISRPEND

Reserved

VTPNDING[8:4]

15

14

13

12

11

10

9

8

VTPEND[3:0]

Reserved

VTACT[8]

7

6

5

4

3

2

1

0

VTACT[7:0]

Bits

Description

[31]

NMIPNSET

NMI Pending Set Control

Setting this bit will activate an NMI. Since NMI is the highest priority exception, it will activate

as soon as it is registered. Reads back with current state (1 if Pending, 0 if not).

[20:29]

Reserved

[28]

PPSVISET

Set a Pending PendSV Interrupt

This is normally used to request a context switch. Reads back with current state (1 if Pending,

0 if not).

[27]

PPSVICLR

Clear a Pending PendSV Interrupt

Write 1 to clear a pending PendSV interrupt.

[26]

PSTKISET

Set a Pending SYST

Reads back with current state (1 if Pending, 0 if not).

[25]

PSTKICLR

Clear a Pending SYST

Write 1 to clear a pending SYST.

[23]

ISRPREEM

ISR Preemptive

If set, a pending exception will be serviced on exit from the debug halt state.

[22]

ISRPEND

ISR Pending

Indicates if an external configurable (NVIC generated) interrupt is pending.

[21]

Reserved

[20:12]

VTPEND

Vector Pending

Indicates the exception number for the highest priority pending exception. The pending state

includes the effect of memory-mapped enable and mask registers. It does not include the

PRIMASK special-purpose register qualifier. A value of zero indicates no pending exceptions.

[11:9]

Reserved