ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 151 -

Revision 2.4

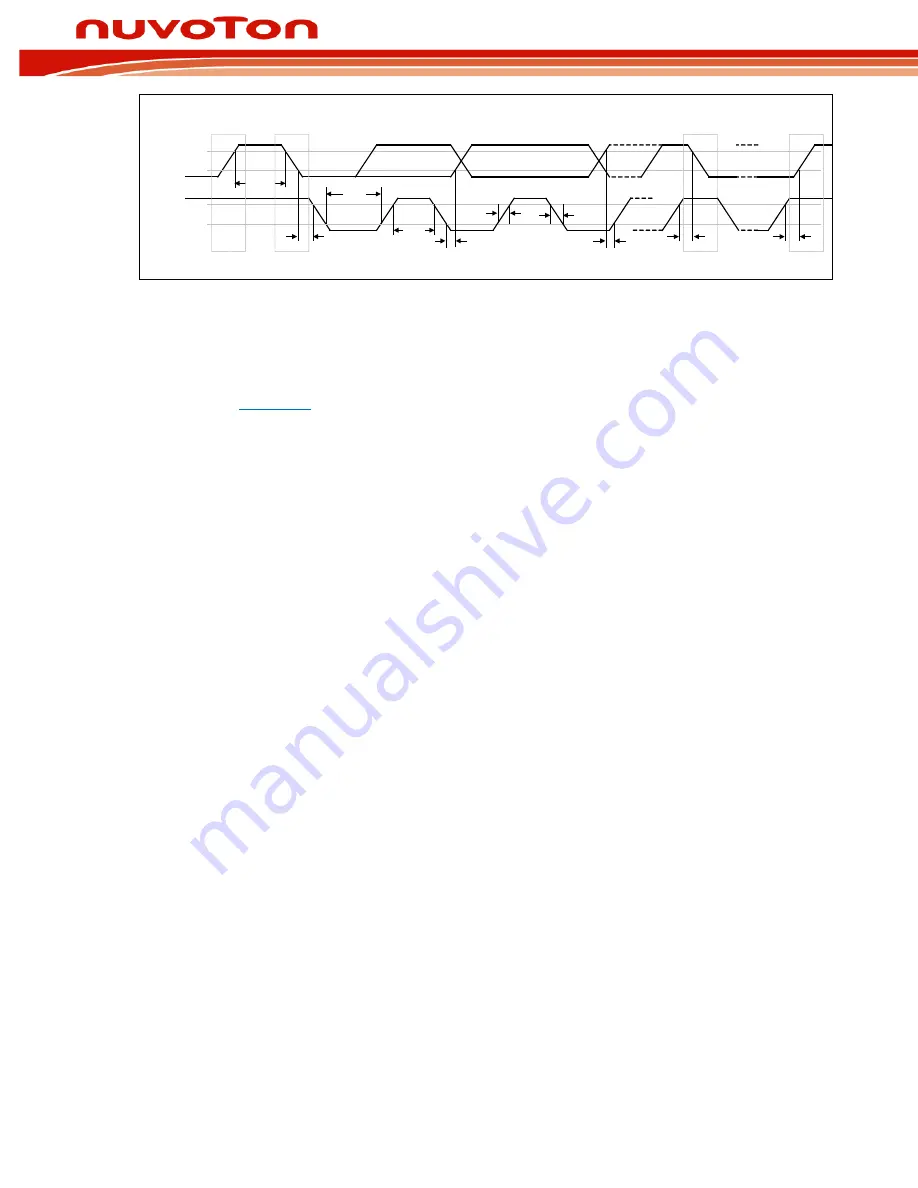

t

BUF

S TOP

S DA

S CL

S TART

t

HD;S TA

t

LO W

t

HD;DAT

t

HIG H

t

f

t

S U;DAT

Re pe a te d

S TART

t

S U;S TA

t

S U;S TO

S TOP

t

r

Figure 5-9 I2C Bus Timing

The device’s on-chip I2C logic provides the serial interface that meets the I2C bus standard mode

specification. The I2C port handles byte transfers autonomously. To enable this port, the bit I2CEN in

I2C_CTL should be set to '1'. The I2C H/W interfaces to the I2C bus via two pins: I2C_SDA and

I2C_SCL.See

for alternate GPIO pin functions. Pull up resistor is needed for these pins for

I2C operation as these are open drain pins.

The I2C bus uses two wires (SDA and SCL) to transfer information between devices connected to the

bus. The main features of the bus are:

Master/Slave up to 1Mbit/s

Bidirectional data transfer between masters and slaves

Multi-master bus (no central master)

Arbitration between simultaneously transmitting masters without corruption of serial data on the

bus

Serial clock synchronization allows devices with different bit rates to communicate via one serial

bus

Serial clock synchronization can be used as a handshake mechanism to suspend and resume

serial transfer

Built-in a 14-bit time-out counter will request the I2C interrupt if the I2C bus hangs up and timer-

out counter overflows.

External pull-up are needed for high output

Programmable clocks allow versatile rate control

Supports 7-bit addressing mode

I2C-bus controllers support multiple address recognition ( Four slave address with mask option)

5.6.1.1

I

2

C Protocol

Normally, a standard communication consists of four parts:

1) START or Repeated START signal generation

2) Slave address transfer

3) Data transfer

4) STOP signal generation