ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 62 -

Revision 2.4

IRQ0 ~ IRQ31 Set-Enable Control Register

(

NVIC_ISER

)

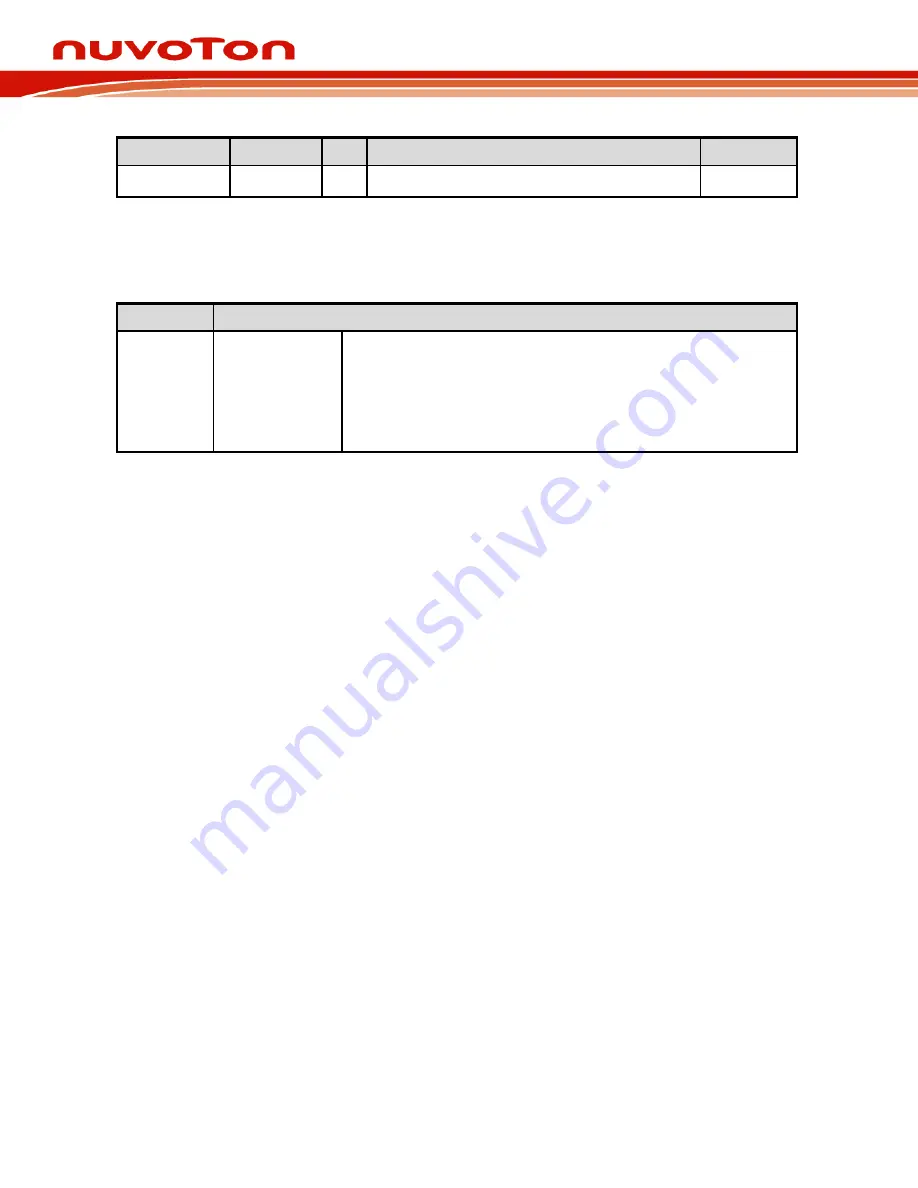

Register

Offset

R/W

Description

Reset Value

NVIC_ISER

0x000 R/W

IRQ0 ~ IRQ31 Set-Enable Control Register

0x0000_0000

If a pending interrupt is enabled, the NVIC activates the interrupt based on its priority. If an interrupt is

not enabled, asserting its interrupt signal changes the interrupt state to pending, but the NVIC never

activates the interrupt, regardless of its priority.

Table 5-24 Interrupt Set-Enable Control Register (ISER, address 0xE000_E100) Bit Description

Bits

Description

[31:0]

SETENA

Set-enable Control

Enable one or more interrupts within a group of 32. Each bit represents an interrupt

number from IRQ0 ~ IRQ31 (Vector number from 16 ~ 47).

Writing 1 will enable the associated interrupt.

Writing 0 has no effect.

The register reads back the current enable state.