ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 272 -

Revision 2.4

[31:0]

TX

Data Transmit Register

The Data Transmit Registers hold the data to be transmitted in the next

transfer. Valid bits depend on the transmit bit length field in the SPI1_CTL

register. For example, if TXBITLEN is set to 0x08 and the TXNUM is set to

0x0, the bit SPI1_TX0[7:0] will be transmitted in next transfer. If TXBITLEN

is set to 0x00 and TXNUM is set to 0x1, the core will perform two 32-bit

transmit/receive successive using the same setting (the order is

SPI1_TX0[31:0], SPI1_TX1[31:0]).

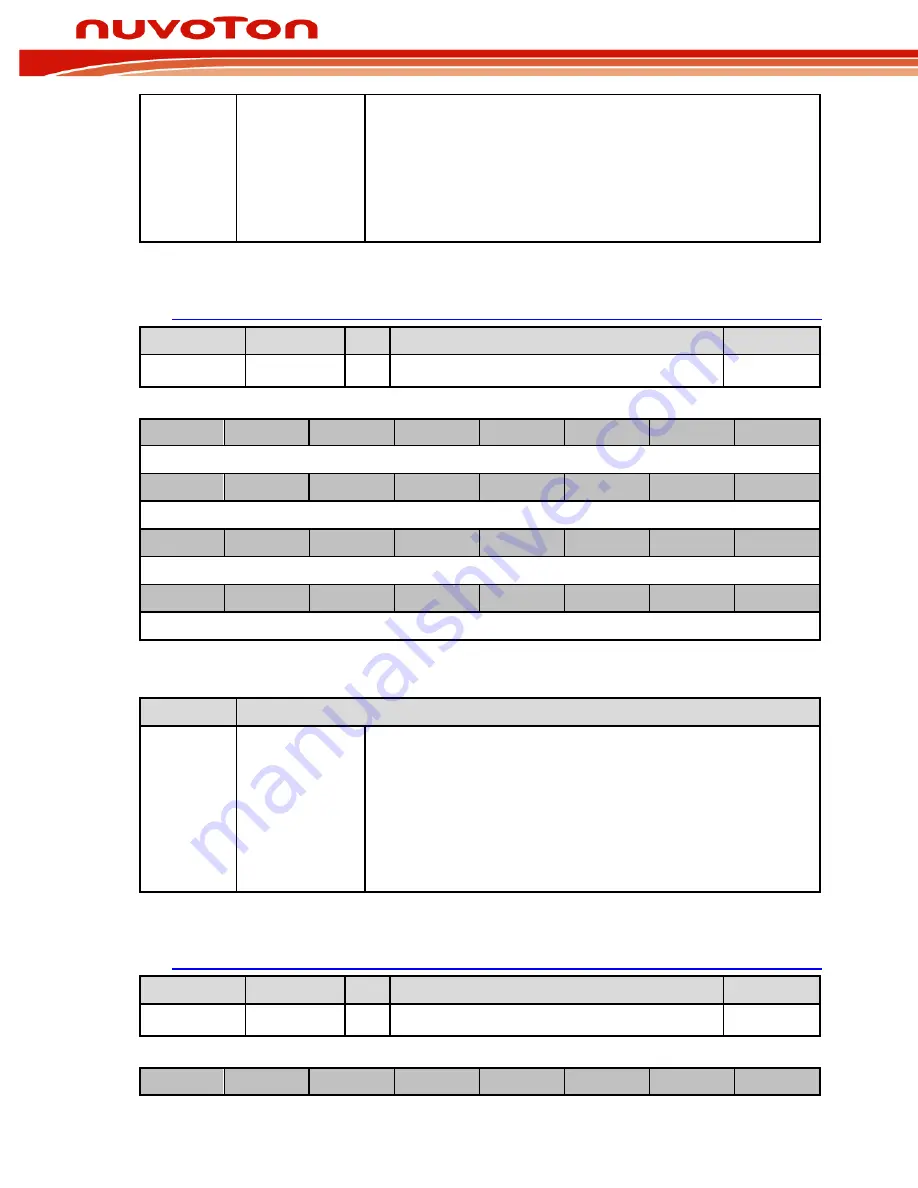

SPI Variable Clock Pattern Flag Register (VARCLK)

Register

Offset

R/W

Description

Reset Value

SPI1_VARCLK

S 0x34 R/W

Variable Clock Pattern Register

0x007F_FF87

31

30

29

28

27

26

25

24

VARCLK

23

22

21

20

19

18

17

16

VARCLK

15

14

13

12

11

10

9

8

VARCLK

7

6

5

4

3

2

1

0

VARCLK

Table 5-108 SPI Variable Clock Pattern Register (VARCLK, address 0x4003_8034)

Bits

Description

[31:0]

VARCLK

Variable Clock Pattern

The value in this field is the frequency pattern of the SPI clock. If the bit

field of VARCLK is ‘0’, the output frequency of SCLK is given by the value

of DIVIDER. If the bit field of VARCLK is ‘1’, the output frequency of SCLK

is given by the value of CLKDIV1. Refer to register CLKDIV0.

Refer to Figure 5-62 Variable Serial Clock Frequency paragraph for

detailed description.

Note: Used for CLKP = 0 only, 16 bit transmission.

DMA Control Register (DMA)

Register

Offset

R/W

Description

Reset Value

SPI1_PDMACTL

S 0x38 R/W

SPI PDMA Control Register

0x0000_0000

31

30

29

28

27

26

25

24