ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 400 -

Revision 2.4

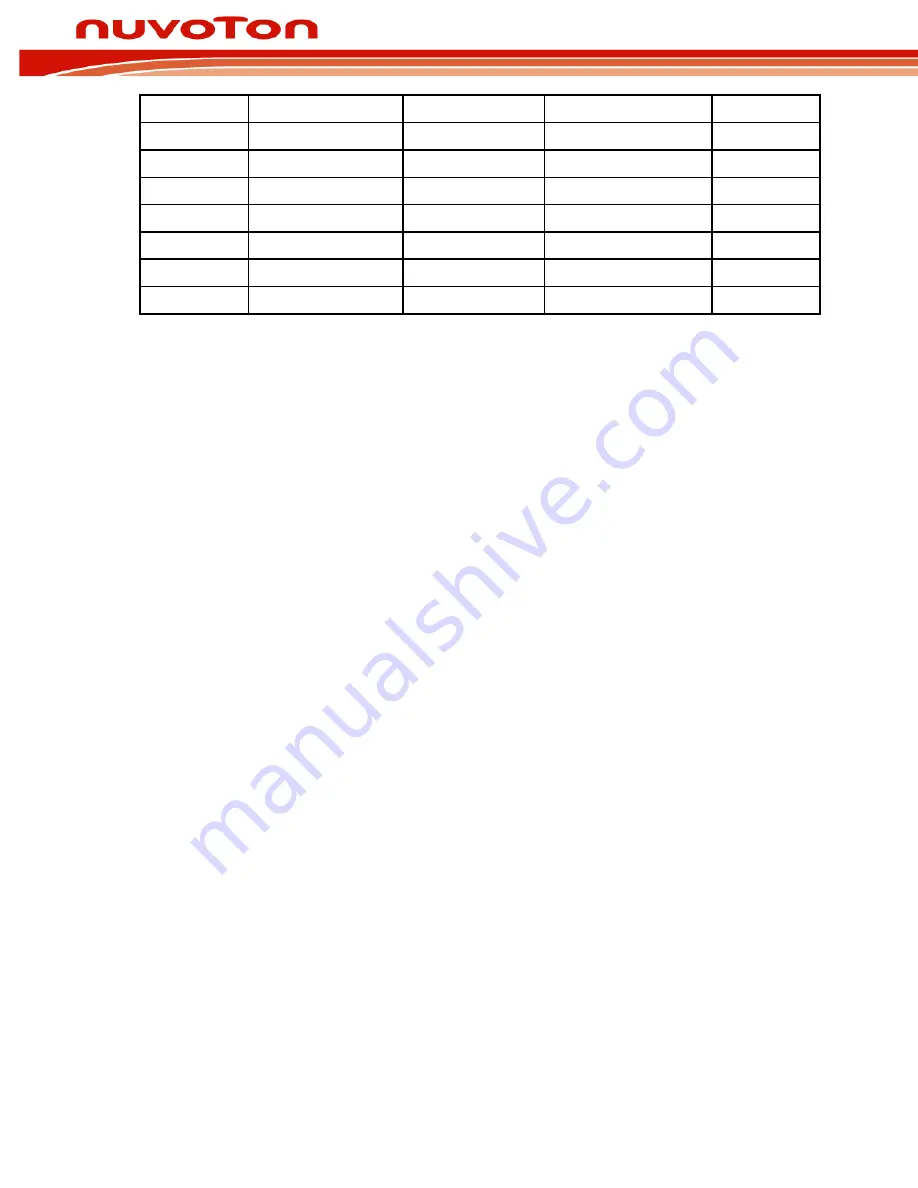

16KHz

24

off

1x

64

12

on

2x

128

6

on

4x

256

4

on

6x

384

8KHz

48

off

1x

64

24

on

2x

128

12

on

4x

256

8

on

6x

384

7.3.4.4

Configuring Speaker Driver

To operate the speaker driver the following configuration is recommended:

•

Enable DPWM clock source (CLK_APBCLK0.DPWMCKEN, CLK_CLKSEL1.DPWMCKSEL).

•

Reset DPWM IP block. (SYS_IPRST1.DPWMRST)

•

Select sample rate based on current DPWM_CLK frequency.

•

Setup PDMA channel to provide data to DPWM.

•

Enable PDMA Request.

•

Enable Driver.

To operate the speaker driver the following configuration is recommended with BIQ and Volume control.

•

Enable DPWM clock source (APBCLK0.DPWMCKEN, CLKSEL1.DPWMSEL).

•

Reset DPWM IP block. (IPRST1.DPWMRST,IPRST1.BIQ_RST).

•

Enable BIQ clock source (APBCLK0.BIQALCEN).

•

Enable BIQ on DPWM path (BIQ_CTL.PATHSEL, BIQ_CTL.BIQEN,

BIQ_CTL.DPWMPUSR, BIQ_CTL.STAGE, BIQ_CTL.HPFON).

•

Set BIQ coefficient(BIQ_COEFF)

•

Setup DPWM volume control (VOLCTRL_EN.DPWMVOLEN,VOLCTRL_DPWMVAL).

(note: setup BIQ_CTL.DLCOEFF =1 and BIQ enable BIQ_CTL.BIQEN =1 for BIQ operation).

•

Select sample rate based on current DPWM_CLK frequency and set ZOHDIV

•

Setup PDMA channel to provide data to DPWM.

•

Enable PDMA Request.

•

Enable DPWM IP (DPWM_CTL.DPWMEN).

7.3.4.5

Peripheral DMA Request

Normal use of the DPWM is with PDMA. In this mode DPWM requests PDMA service whenever there

is space in FIFO. PDMA channel will copy data from a streaming buffer to the DPWM and alert the CPU

when buffer is empty. In this way an entire buffer of data can be sent to DPWM without any CPU

intervention.