ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 141 -

Revision 2.4

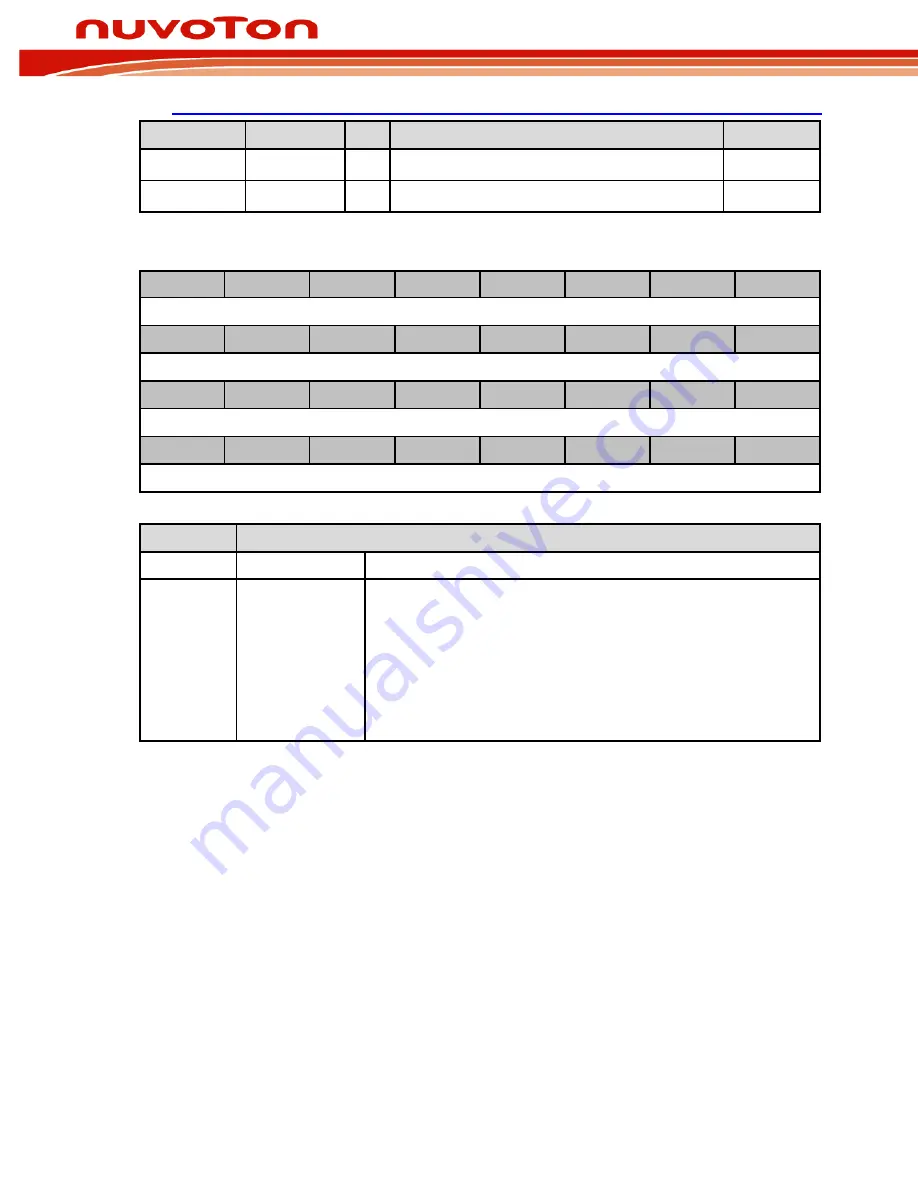

GPIO Port [A/B] De-bounce Enable (Px _DBEN)

Register

Offset

R/W

Description

Reset Value

PA_DBEN

0x014 R/W

GPIO Port A De-bounce Enable

0xXXXX_0000

PB_DBEN

0x054 R/W

GPIO Port B De-bounce Enable

0xXXXX_0000

Table 5-54 GPIO Debounce Enable Register (Px_DBEN)

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

DBEN[15:8]

7

6

5

4

3

2

1

0

DBEN[7:0]

Bits

Description

[31:16]

Reserved

Reserved.

[15:0]

DBEN

Port [A/B] De-bounce Enable Control

DBEN[n]used to enable the de-bounce function for each corresponding bit. For an

edge triggered interrupt to be generated, input signal must be valid for two

consecutive de-bounce periods. The de-bounce time is controlled by the

GPIO_DBCTL

register.

The DBEN[n] is used for “edge-trigger” interrupt only; it is ignored for “level trigger”

interrupt

0 = The bit[n] de-bounce function is disabled.

1 = The bit[n] de-bounce function is enabled.