ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 145 -

Revision 2.4

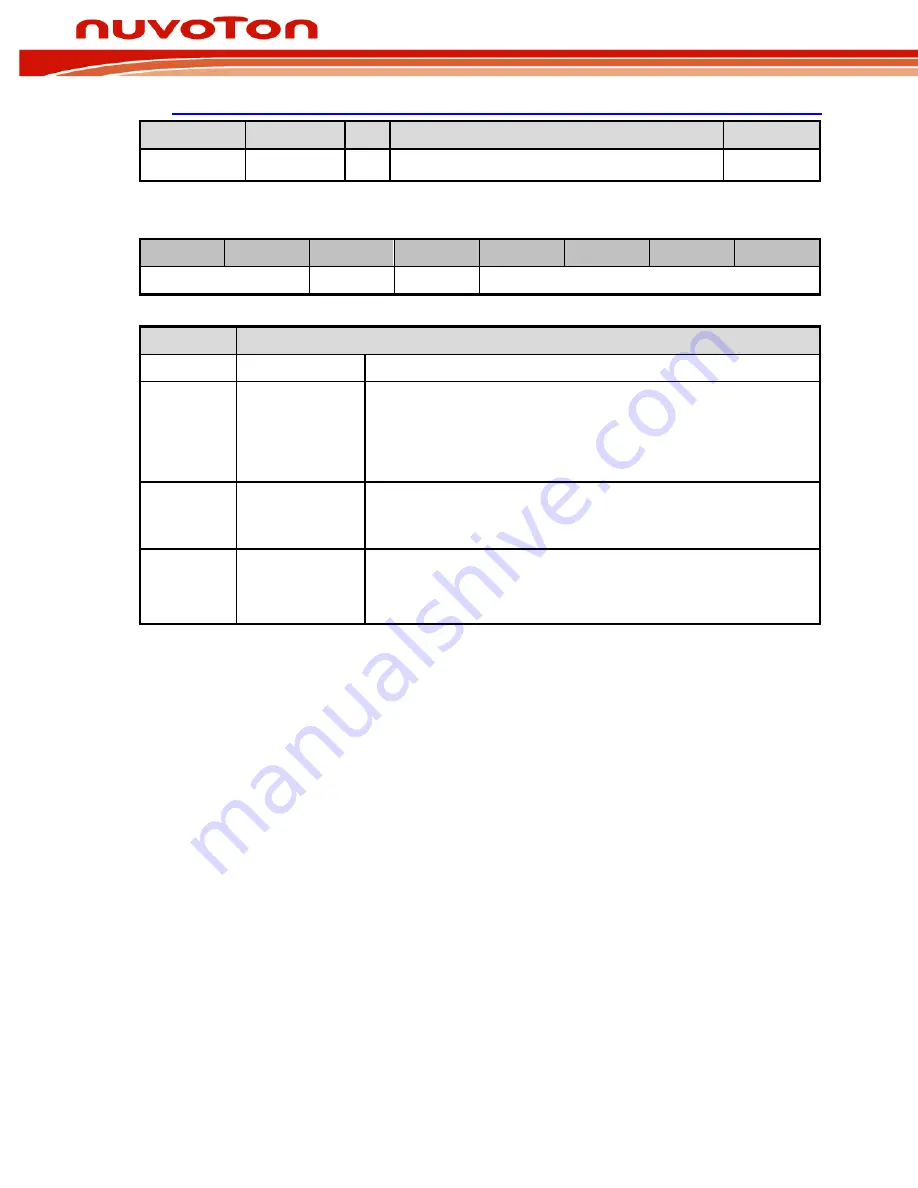

Interrupt De-bounce Control (GPIO_DBCTL )

Register

Offset

R/W

Description

Reset Value

DBCTL

0x180 R/W

Interrupt De-bounce Control

0x0000_0020

Table 5-58 GPIO Interrupt De-bounce Control Register (GPIO_DBCTL )

7

6

5

4

3

2

1

0

Reserved

ICLKON

DBCLKSRC

DBCLKSEL

Bits

Description

[31:6]

Reserved

Reserved.

[5]

ICLKON

Interrupt Clock on Mode

Set this bit “0” will gate the clock to the interrupt generation circuit if the GPIOx[n]

interrupt is disabled.

0 = disable the clock if the GPIOx[n] interrupt is disabled.

1 = Interrupt generation clock always active.

[4]

DBCLKSRC

De-bounce Counter Clock Source Select

0 = De-bounce counter clock source is HCLK.

1 = De-bounce counter clock source is the internal 16 kHz clock.

[3:0]

DBCLKSEL

De-bounce Sampling Cycle Selection

For edge level interrupt GPIO state is sampled every 2^(DBCLKSEL) de-bounce

clocks. For example if DBCLKSRC

= 6, then interrupt is sampled every 2^6 = 64 de-

bounce clocks. If DBCLKSRC

is 10kHz oscillator this would be a 64ms de-bounce.