ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 250 -

Revision 2.4

5.10 Serial 1 Peripheral Interface (SPI1) Controller

5.10.1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial data communication protocol which

operates in full duplex mode. Devices communicate in master/slave mode with 4-wire bi-directional

interface. The I91200 contains an SPI controller performing a serial-to-parallel conversion of data

received from an external device, and a parallel-to-serial conversion of data transmitted to an external

device. The SPI1 controller can be set as a master; also can be set as a slave controlled by an off-chip

master device.

5.10.2 Features

Supports master or slave mode operation.

Configurable word length of up to 32 bits. Up to two words can be transmitted per a transaction,

giving a maximum of 64 bits for each data transaction.

Provide burst mode operation.

MSB or LSB first transfer.

2 device/slave select lines in master mode, single device/slave select line in slave mode.

Byte or word Sleep Suspend Mode .

Support dual FIFO mode.

PDMA access support.

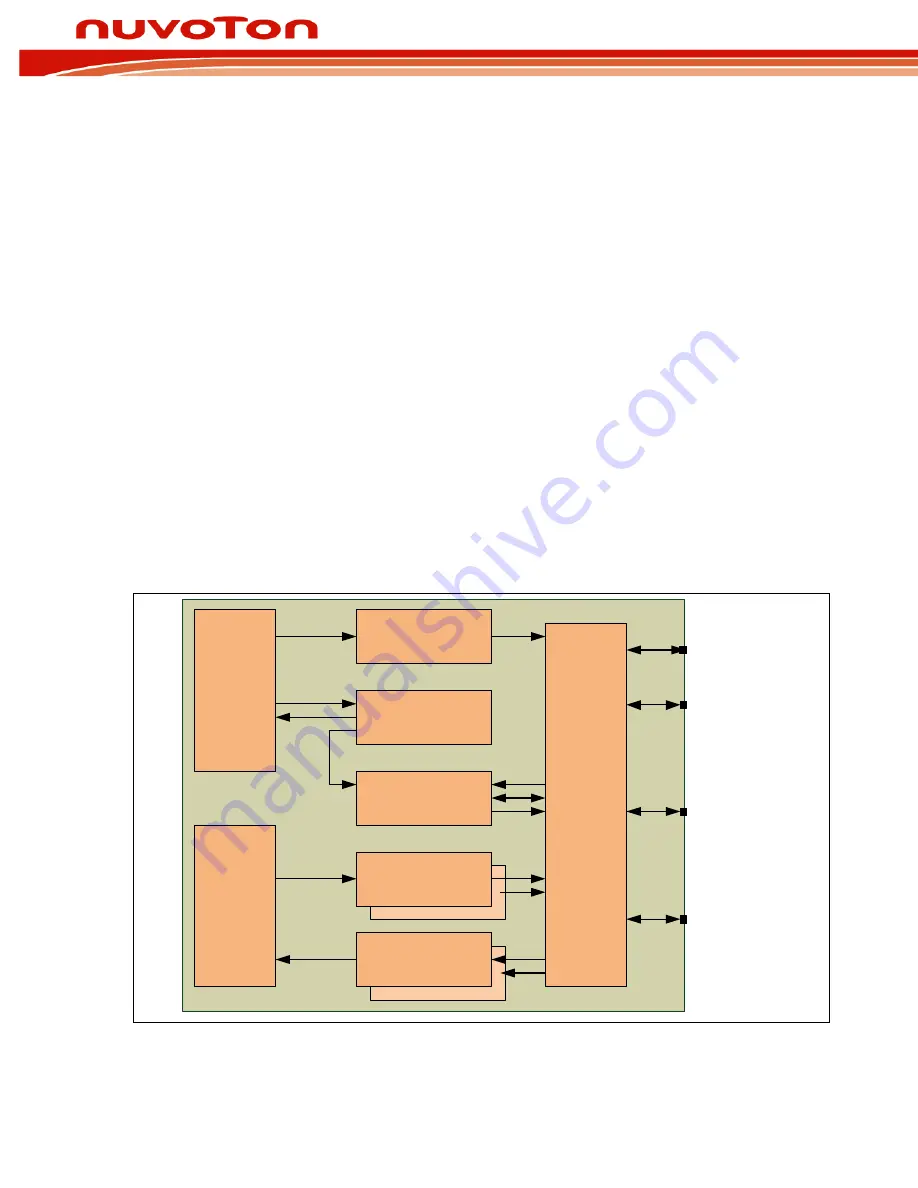

5.10.3 SPI1 Block Diagram

APB

IF

(32-bits)

PDMA

Control

Clock Generator

Status/Control

Register

Core Logic

TX Bufer/

Shifter

RX Bufer/

Shifter

TX Bufer/

Shifter

RX Bufer/

Shifter

PIO

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSB

Figure 5-52 SPI1 Block Diagram