ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 303 -

Revision 2.4

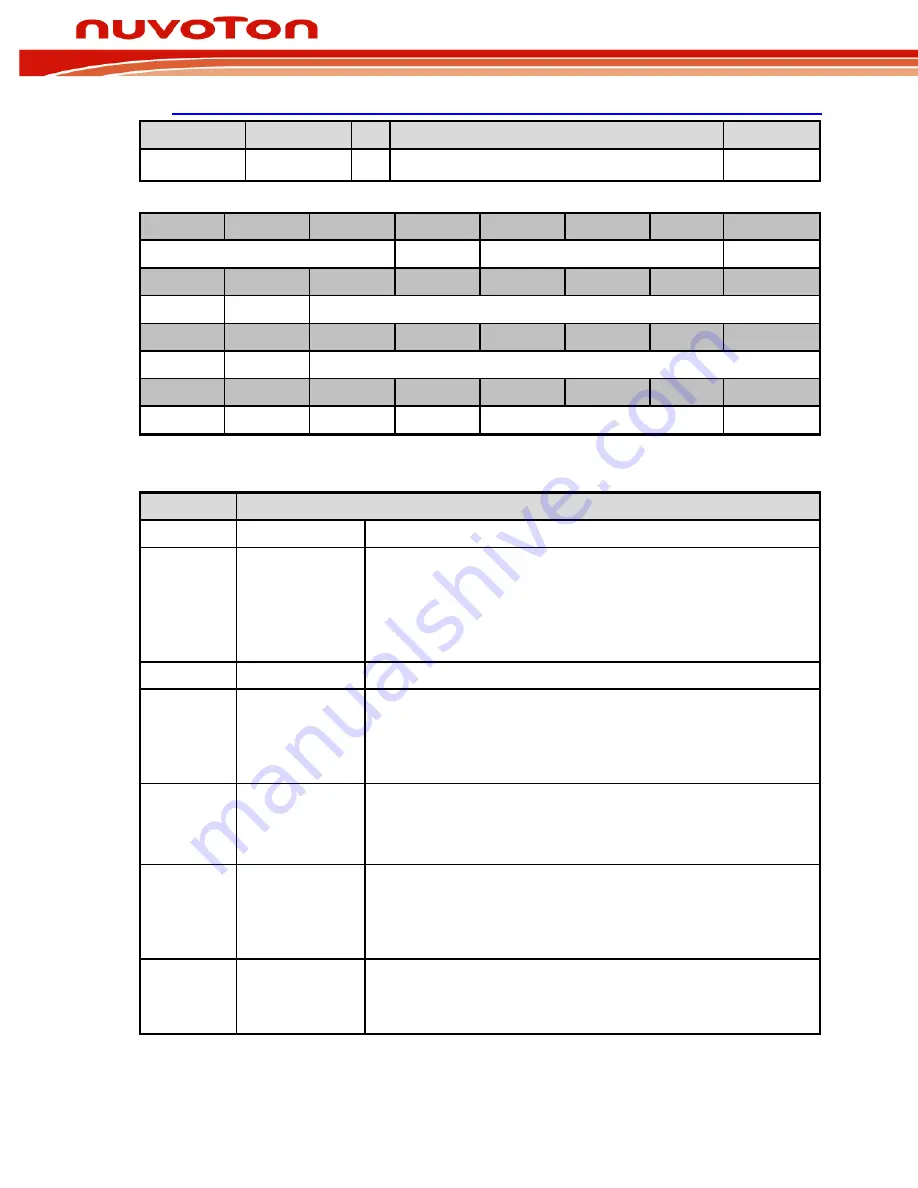

FIFO Status Register (UARTn_FIFOSTS)

Register

Offset

R/W

Description

Reset Value

UARTn_FIFOSTS

U0x18 R/W

UART FIFO Status Register.

0x1040_4000

31

30

29

28

27

26

25

24

Reserved

TXEMPTYF

Reserved

TXOVIF

23

22

21

20

19

18

17

16

TXFULL

TXEMPTY

TXPTR

15

14

13

12

11

10

9

8

RXFULL

RXEMPTY

RXPTR

7

6

5

4

3

2

1

0

Reserved

BIF

FEF

PEF

Reserved

RXOVIF

Table 5-123 UART FIFO Status Register (UARTn_FIFOSTS, address 0x4005_0018)

Bits

Description

[31:29]

Reserved

Reserved.

[28]

TXEMPTYF

Transmitter Empty (Read Only)

Bit is set by hardware when Tx FIFO is empty and the STOP bit of the last byte has

been transmitted.

Bit is cleared automatically when Tx FIFO is not empty or the last byte transmission

has not completed.

NOTE: This bit is read only.

[27:25]

Reserved

Reserved.

[24]

TXOVIF

Tx Overflow Error Interrupt Flag

If the Tx FIFO (UART_DAT) is full, an additional write to UART_DAT will cause an

overflow condition and set this bit to logic 1. It will also generate a BUFERRIF event

and interrupt if enabled.

NOTE: This bit is cleared by writing 1 to itself.

[23]

TXFULL

Transmit FIFO Full (Read Only)

This bit indicates whether the Tx FIFO is full or not.

This bit is set when Tx FIFO is full; otherwise it is cleared by hardware. TXFULL=0

indicates there is room to write more data to Tx FIFO.

[22]

TXEMPTY

Transmit FIFO Empty (Read Only)

This bit indicates whether the Tx FIFO is empty or not.

When the last byte of Tx FIFO has been transferred to Transmitter Shift Register,

hardware sets this bit high. It will be cleared after writing data to FIFO (Tx FIFO not

empty).

[21:16]

TXPTR

Tx FIFO Pointer (Read Only)

This field returns the Tx FIFO buffer pointer. When CPU writes a byte into the Tx

FIFO, TXPTR is incremented. When a byte from Tx FIFO is transferred to the

Transmit Shift Register, TXPTR is decremented.