ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 247 -

Revision 2.4

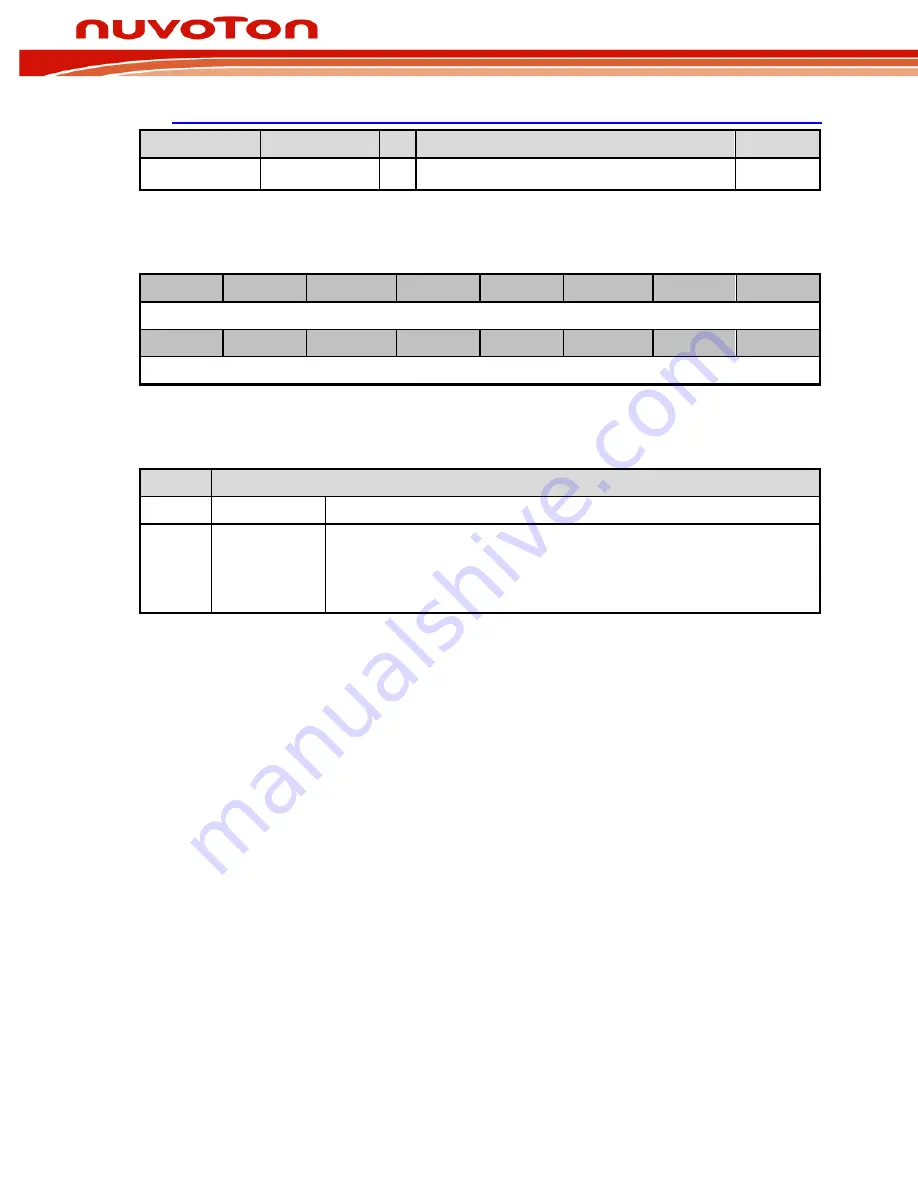

SPI Receive Transaction Count (SPI0_RXTSNCNT)

Register

Offset

R/W Description

Reset Value

SPI0_RXTSNCNT

S 0x18

R/W Receive Transaction Count Register

0x0000_0000

Table 5-97 SPI Receive Transaction Count (address S 0x18)

15

14

13

12

11

10

9

8

RXTSNCNT

7

6

5

4

3

2

1

0

RXTSNCNT

Table 5-98 SPI Receive Transaction Count (SPI0_RXTSNCNT, address S 0x18)

Bits

Description

[31:16]

Reserved

Reserved.

[16:0]

RXTSNCNT

DMA Receive Transaction Count

When using DMA to receive SPI data without transmitting data, this register can be used in

conjunction with the control bit SPI0_CTL.RXTCNTEN to set number of transactions to

perform. Without this, the SPI interface will only initiate a transaction when it receives a

request from the DMA system, resulting in a lower achievable data rate.