ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 167 -

Revision 2.4

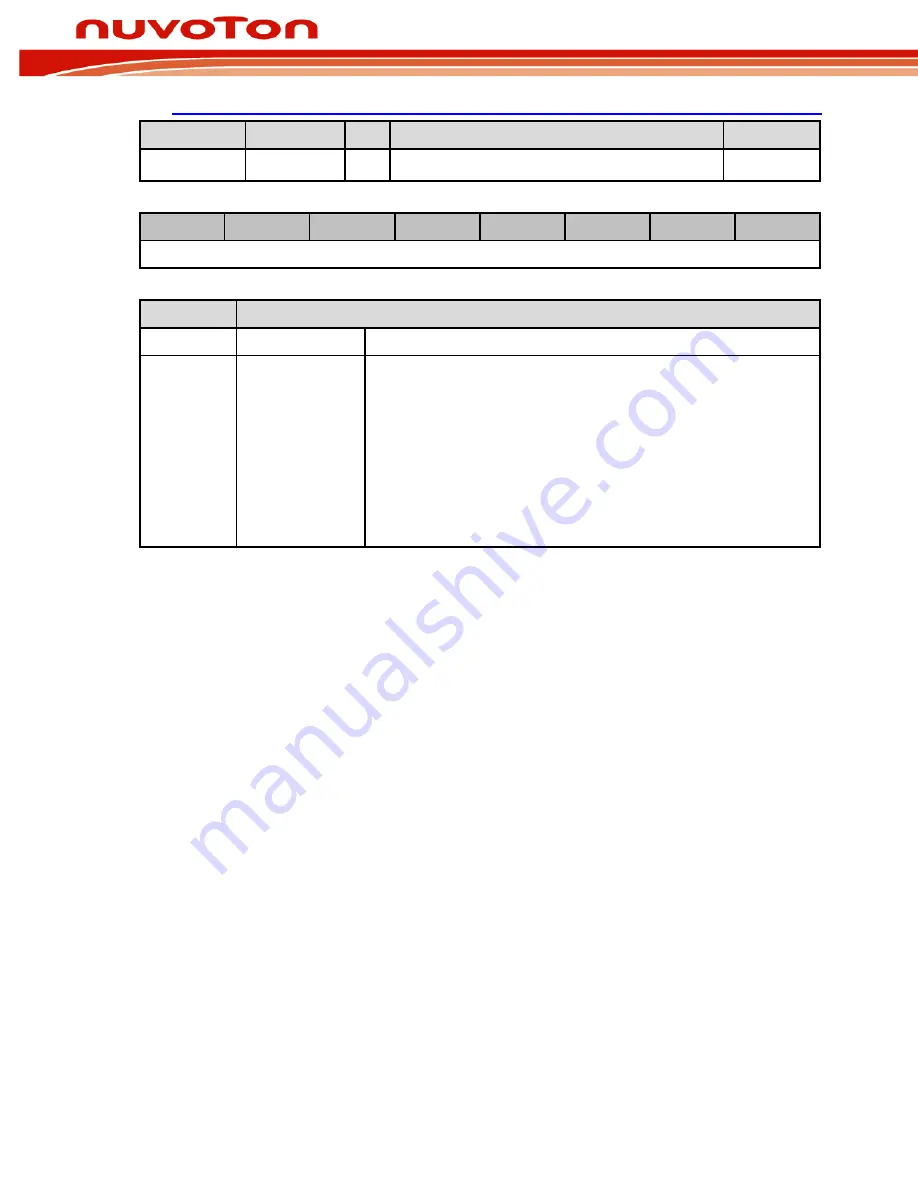

I2C STATUS REGISTER (I2C_STATUS )

Register

Offset

R/W

Description

Reset Value

I2C_STATUS

0x0C

R

I2C Status Register

0x0000_00F8

7

6

5

4

3

2

1

0

STATUS[7:0]

Bits

Description

[31:8]

Reserved

Reserved.

[7:0]

STATUS

I2C Status Register

The status register of I2C:

The three least significant bits are always 0. The five most significant bits contain the

status code. There are 26 possible status codes. When I2C_STATUS contains F8H,

no serial interrupt is requested. All other I2C_STATUS values correspond to defined

I2C states. When each of these states is entered, a status interrupt is requested (SI

= 1). A valid status code is present in I2C_STATUS one PCLK cycle after SI is set by

hardware and is still present one PCLK cycle after SI has been reset by software. In

addition, states 00H stands for a Bus Error. A Bus Error occurs when a START or

STOP condition is present at an illegal position in the frame. Example of illegal

position are during the serial transfer of an address byte, a data byte or an

acknowledge bit.