MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

89

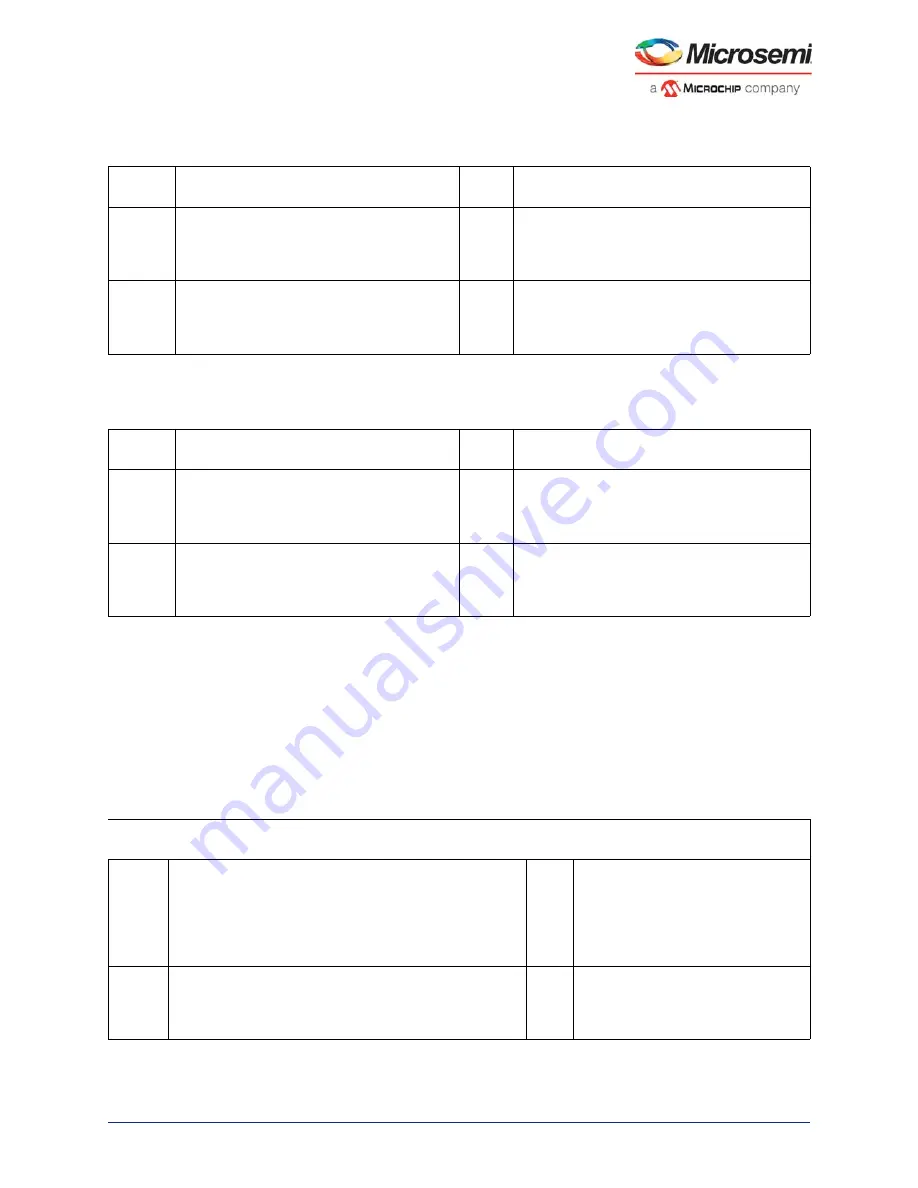

Table 74 •

DDRC_DFI_MIN_CTRLUPD_TIMING_CR

Bit

Number

Name

Reset

Value

Description

[31:10]

Reserved

0×0

Software should not rely on the value of a

reserved bit. To provide compatibility with future

products, the value of a reserved bit should be

preserved across a read-modify-write operation.

[9:0]

REG_DDRC_DFI_T_CTRLUP_MIN

0×03

Specifies the minimum number of clock cycles

that the DDRC_DFI_CTRLUPD_REQ signal

must be asserted. Lowest value to assign to this

variable is 0x3. Units: Clocks

Table 75 •

DDRC_DFI_MAX_CTRLUPD_TIMING_CR

Bit

Number

Name

Reset

Value

Description

[31:10]

Reserved

0×0

Software should not rely on the value of a

reserved bit. To provide compatibility with future

products, the value of a reserved bit should be

preserved across a read-modify-write operation.

[9:0]

REG_DDRC_DFI_T_CTRLUP_MAX

0×40

Specifies the maximum number of clock cycles

that the DDRC_DFI_CTRLUPD_REQ signal can

assert. Lowest value to assign to this variable is

0x40. Units: Clocks

Table 76 •

DDRC_DYN_SOFT_RESET_ALIAS_CR

Bit

Number Name

Reset

Value Description

[31:3]

Reserved

0×0

Software should not rely on the value

of a reserved bit. To provide

compatibility with future products, the

value of a reserved bit should be

preserved across a read-modify-write

operation.

2

AXIRESET

0×1

Set when main AXI reset signal is

asserted. Reads and writes to the

dynamic registers should not be

carried out. This is a read only bit.