Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

142

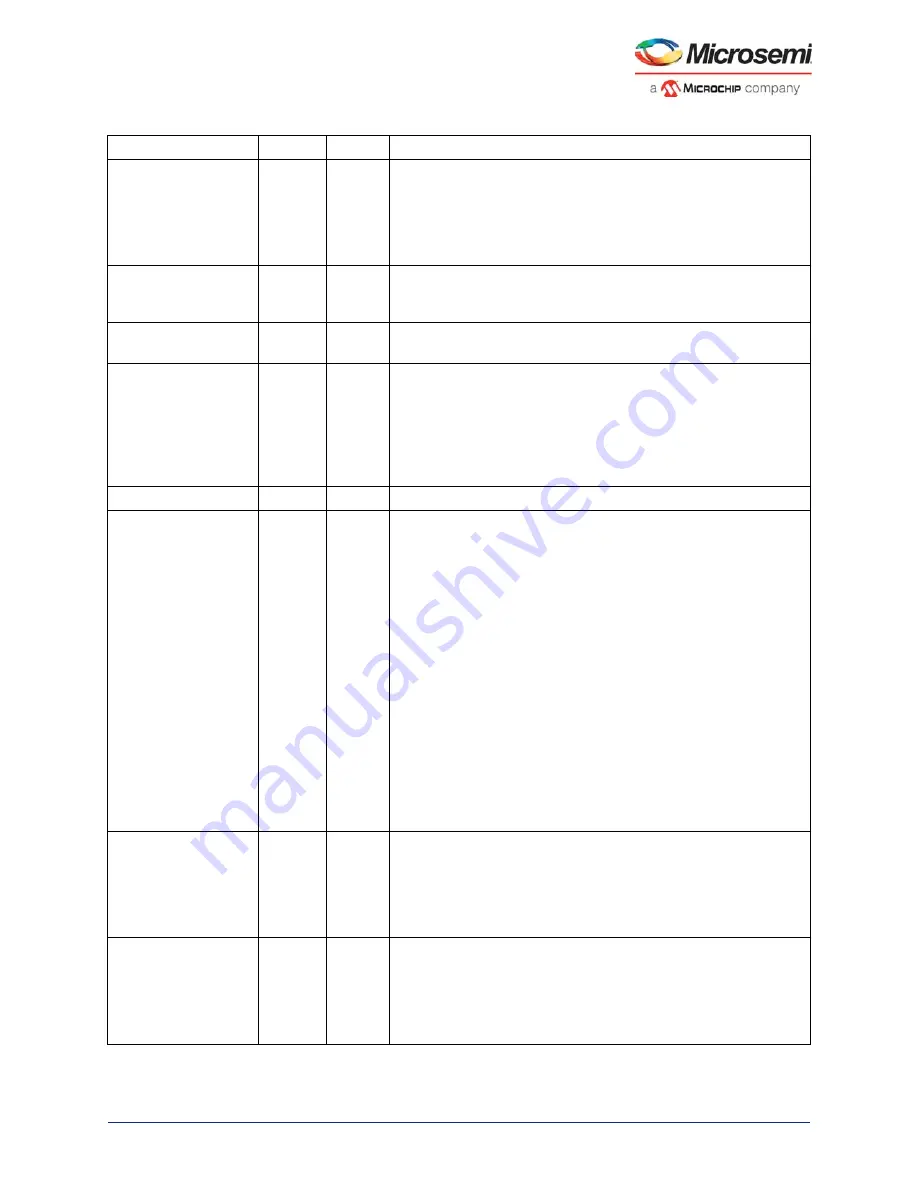

AXI_S_ARSIZE[1:0]

Input

Indicates the maximum number of data bytes to transfer in each data

transfer, within a burst.

00: 1

01: 2

10: 4

11: 8

AXI_S_ARVALID

Input

High

Indicates the validity of read address and control information.

1: Address and control information valid

0: Address and control information not valid

AXI_S_AWADDR[31:0] Input

Indicates write address. The write address bus gives the address of

the first transfer in a write burst transaction.

AXI_S_AWBURST[1:0] Input

Indicates burst type. The burst type, coupled with the size information,

details how the address for each transfer within the burst is calculated.

00: FIXED - Fixed-address burst FIFO-type

01: INCR - Incrementing-address burst normal sequential memory

10: WRAP - Incrementing-address burst that wraps to a lower address

at the wrap boundary

11: Reserved

AXI_S_AWID[3:0]

Input

Indicates identification tag for the write address group of signals.

AXI_S_AWLEN[3:0]

Input

Indicates burst length. The burst length gives the exact number of

transfers in a burst. This information determines the number of data

transfers associated with the address.

0000: 1

0001: 2

0010: 3

0011: 4

0100: 5

0101: 6

0110: 7

0111: 8

1000: 9

1001: 10

1010: 11

1011: 12

1100: 13

1101: 14

1110: 15

1111: 16

AXI_S_AWLOCK[1:0]

Input

Indicates lock type. This signal provides additional information about

the atomic characteristics of the write transfer.

00: Normal access

01: Exclusive access

10: Locked access

11: Reserved

AXI_S_AWSIZE[1:0]

Input

Indicates the maximum number of data bytes to transfer in each data

transfer, within a burst.

00: 1

01: 2

10: 4

11: 8

Table 129 •

FDDR AXI Slave Interface Signals

(continued)

Signal Name

Direction Polarity Description