MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

106

[31:10]

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

[9:0]

DDR_FIC_TIMER

0×0

10-bit timer interface used to configure timeout register. Once timer

reaches the timeout value, a flush request is generated by the flush

controller in the DDR_FIC. This port is common for all buffers.

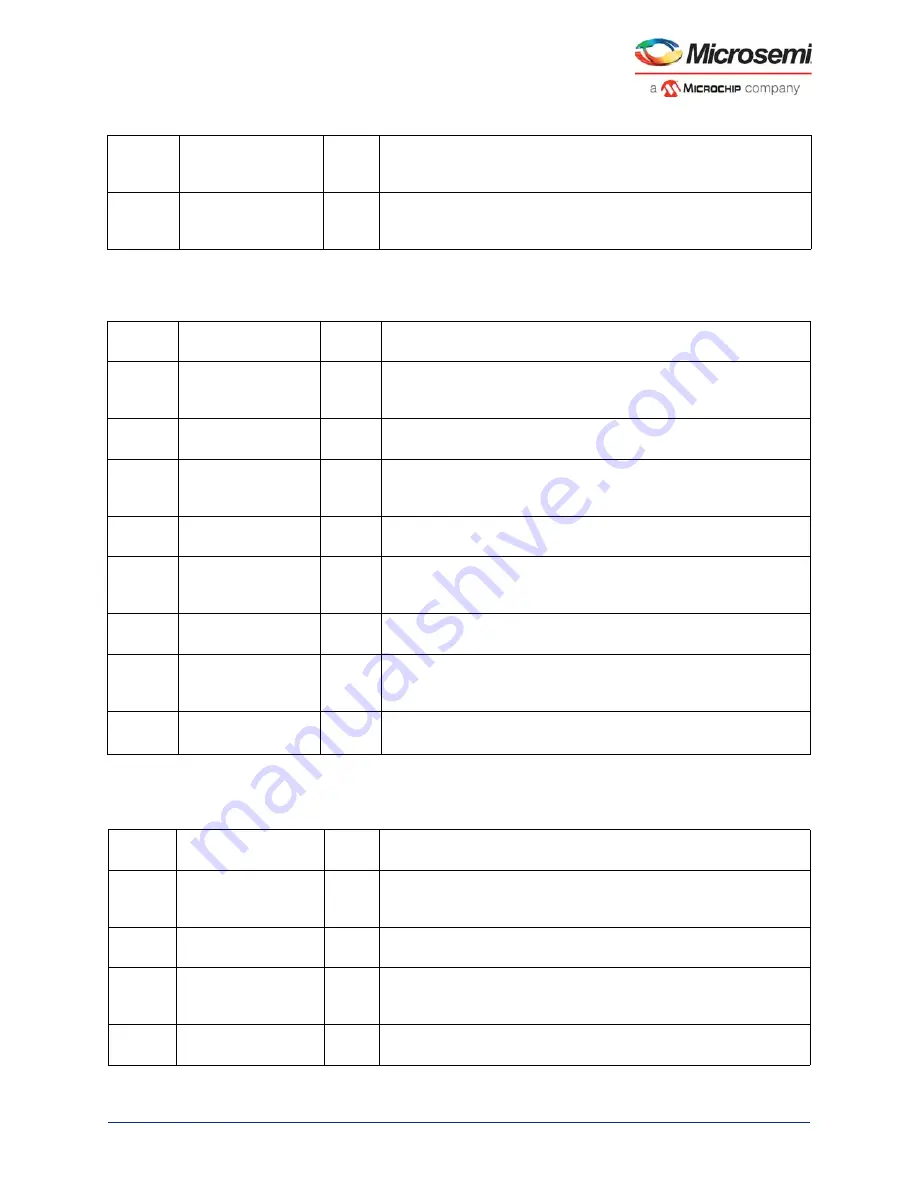

Table 108 •

DDR_FIC_HPD_SW_RW_EN_CR

Bit

Number

Name

Reset

Value

Description

[31:7]

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

6

DDR_FIC_M1_REN

0×0

1: Enable read buffer for AHBL master1.

0: Disable read buffer for AHBL master1.

5

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

4

DDR_FIC_M1_WEN

0×0

1: Enable write buffer for AHBL master1.

0: Disable write buffer for AHBL master1.

3

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

2

DDR_FIC_M2_REN

0×0

1: Enable read buffer for AHBL master2.

0: Disable read buffer for AHBL master2.

1

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

0

DDR_FIC_M2_WEN

0×0

1: Enable write buffer for AHBL master2.

0: Disable write buffer for AHBL master2.

Table 109 •

DDR_FIC_HPD_SW_RW_INVAL_CR

Bit

Number

Name

Reset

Value

Description

[31:7]

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

6

DDR_FIC_flshM1

0×0

1: Flush read buffer for AHBL master1.

0: Default

5

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

4

DDR_FIC_invalid_M1

0×0

1: Invalidate write buffer for AHBL master1.

0: Default

Table 107 •

DDR_FIC_BUF_TIMER_CR