MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

86

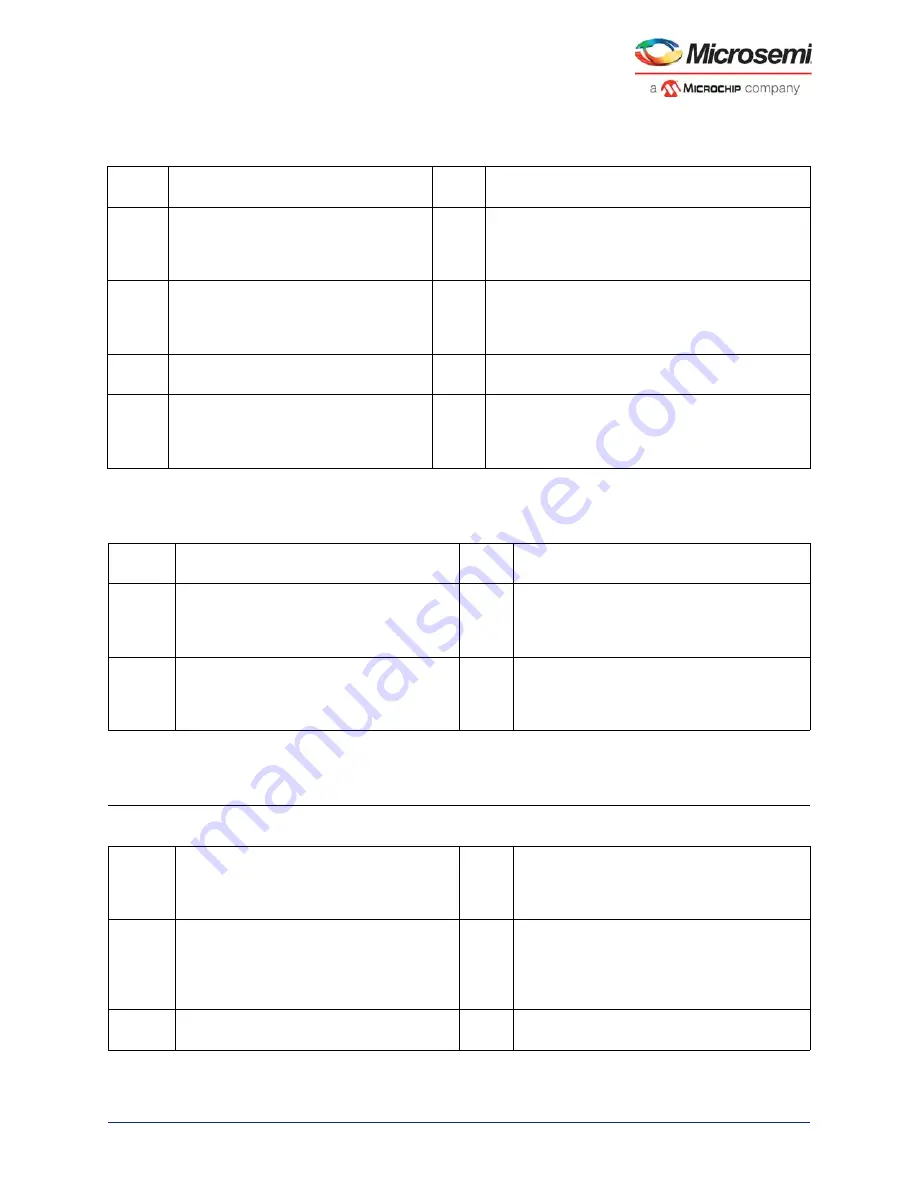

Table 66 •

DDRC_HPR_QUEUE_PARAM_1_CR

Bit

Number Name

Reset

Value

Description

[31:16]

Reserved

0×0

Software should not rely on the value of a reserved

bit. To provide compatibility with future products, the

value of a reserved bit should be preserved across a

read-modify-write operation.

15

REG_DDRC_HPR_MAX_STARVE_X32

0×0

Lower 1 bit of

REG_DDRC_HPR_MAX_STARVE_X32.

Number of clocks that the HPR queue can be starved

before it goes critical. Unit: 32 clocks.

[14:4]

REG_DDRC_HPR_MIN_NON_CRITICAL 0×0

Number of clocks that the HPR queue is guaranteed

to be non-critical. Unit: 32 clocks.

[3:0]

REG_DDRC_HPR_XACT_RUN_LENGTH 0×0

Number of transactions that are serviced once the

HPR queue goes critical is the smaller of this value

and number of transactions available.

Units: Transactions.

Table 67 •

DDRC_HPR_QUEUE_PARAM_2_CR

Bit

Number

Name

Reset

Value

Description

[31:11]

Reserved

0×0

Software should not rely on the value of a

reserved bit. To provide compatibility with future

products, the value of a reserved bit should be

preserved across a read-modify-write operation.

[10:0]

REG_DDRC_HPR_MAX_STARVE_X32

0×0

[11:1] bits of

REG_DDRC_HPR_MAX_STARVE_X32

Number of clocks that the HPR queue can be

starved before it goes critical. Unit: 32 clocks.

Table 68 •

DDRC_LPR_QUEUE_PARAM_1_CR

Bit

Number

Name

Reset

Value

Description

[31:16]

Reserved

0×0

Software should not rely on the value of a

reserved bit. To provide compatibility with future

products, the value of a reserved bit should be

preserved across a read-modify-write operation.

15

REG_DDRC_LPR_MAX_STARVE_X32

0×0

12 bits are split into two registers.

Lower 1 bit of

REG_DDRC_LPR_MAX_STARVE_X32.

Number of clocks that the LPR queue can be

starved before it goes critical. Unit: 32 clocks.

[14:4]

REG_DDRC_LPR_MIN_NON_CRITICAL

0×0

Number of clocks that the LPR queue is

guaranteed to be non-critical. Unit: 32 clocks.