MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

58

*/INST_MSS_*_IP:F_ARSIZE* \

*/INST_MSS_*_IP:F_AWADDR* \

*/INST_MSS_*_IP:F_AWBURST* \

*/INST_MSS_*_IP:F_AWID* \

*/INST_MSS_*_IP:F_AWLEN* \

*/INST_MSS_*_IP:F_AWLOCK* \

*/INST_MSS_*_IP:F_AWSIZE* \

*/INST_MSS_*_IP:F_WDATA* \

*/INST_MSS_*_IP:F_WID* \

*/INST_MSS_*_IP:F_WLAST \

*/INST_MSS_*_IP:F_WSTRB* \

*/INST_MSS_*_IP:F_BREADY \

*/INST_MSS_*_IP:F_RMW_AXI \

*/INST_MSS_*_IP:F_RREADY \

} ]

/* The following constraints provide a relaxation constraint on the signals of 1 clock period.

*/

set delay2 [ expr 2000/$ddr_clock_frequency ]

set_max_delay $delay2 -to [ get_pins { \

*/INST_MSS_*_IP:F_ARVALID* \

*/INST_MSS_*_IP:F_AWVALID* \

*/INST_MSS_*_IP:F_WVALID \

} ]

3.9

DDR Memory Device Examples

This section describes how to connect DDR memories to IGLOO2 MDDR_PADs with examples.

Note:

For more information on requirement of termination resistors, refer to the Datasheets/Application Notes

of the memory manufacturers.

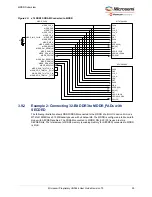

3.9.1

Example 1: Connecting 32-Bit DDR2 to MDDR_PADs

The following illustratoin shows DDR2 SDRAM connected to the MDDR of a IGLOO2 device. Micron’s

MT47H64M16 is a 128 MB density device with x16 data width. The MDDR is configured in full bus width

mode and without SECDED. The total amount of DDR2 memory connected to MDDR is 256 MB.