Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

145

4.6.1.1

DDRIO Calibration

Each DDRIO has an ODT feature, which is calibrated depending on the DDR I/O standard. DDR I/O

calibration occurs after the DDR I/Os are enabled. If the impedance feature is enabled, impedance can

be programmed to the desired value in three ways:

•

Calibrate the ODT/driver impedance with a calibration block (recommended)

•

Calibrate the ODT/driver impedance with fixed calibration codes

•

Configure the ODT/driver impedance to the desired value directly

The I/O calibration is always enabled when the DDR subsystem is configured for DDR2 and DDR3

memories.

The I/O calibration can be disabled or enabled using the DDR configurator when the DDR subsystem is

configured for LPDDR memories.

Note:

If I/O calibration is enabled, all I/Os in the DDR bank are calibrated even though the DDR controller is not

using all I/Os in the bank.

The FDDR_IO_CALIB_CR register can be configured for changing the ODT value to the desired value.

For more information on DDR I/O calibration, refer to the Configurable ODT and Driver Impedance

section of the I/Os chapter in the

UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User

.

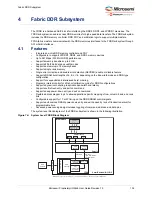

Figure 76 •

Reset Sequence

4.6.2

ZQ Calibration

ZQ calibration is applicable for DDR3 only. This is used to calibrate DRAM output drivers (R

ON

) and on-

die termination (ODT) values. DDR3 SDRAM needs a longer time to calibrate R

ON

and ODT at

initialization and a relatively smaller time to perform periodic calibrations.

The DDR controller performs ZQ calibration by issuing a ZQ calibration long (ZQCL) command and ZQ

calibration short (ZQCS) command.

ZQCL is used to perform initial calibration during the power-up initialization sequence. This command is

allowed for a period of t

ZQinit

, as specified by memory vendor. The value of t

ZQinit

can be modified

through register bits REG_DDRC_T_ZQ_LONG_NOP,

The ZQCS command is used to perform periodic calibration to account for voltage and temperature

variations. A shorter timing window is provided to perform calibration and transfer of values as defined by

timing parameter tZQCS. The t

ZQCS

parameter can be modified through register bits

REG_DDRC_T_ZQ_SHORT_NOP,

PO_RESET_N

APB_S_PRESET_N

DDRIO

Calibration

MSS_RESET_N_M2F

or

HPMS_RESET_N_M2F

FPLL_LOCK

FDDR APB Register

Configuration

CORE_RESET_N