Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

134

4

Fabric DDR Subsystem

The FDDR is a hardened ASIC block for interfacing the DDR2, DDR3, and LPDDR1 memories. The

FDDR subsystem is used to access DDR memories for high-speed data transfers. The FDDR subsystem

includes the DDR memory controller, DDR PHY, and arbitration logic to support multiple masters.

FPGA fabric masters communicate with the DDR memories interfaced to the FDDR subsystem through

AXI or AHB interfaces.

4.1

Features

•

Integrated on-chip DDR memory controller and PHY

•

Configurable to support LPDDR1, DDR2, and DDR3 memory devices

•

Up to 667 Mbps (333 MHz DDR) performance

•

Supports memory densities up to 4 GB

•

Supports 8/16/32-bit data bus width modes

•

Supports a maximum of 8 memory banks

•

Supports single rank memory

•

Single error correction and double error detection (SECDED) enable or disable feature

•

Supports DRAM burst lengths of 4, 8, or 16, depending on the Bus-width mode and DDR type

configuration

•

Support for sequential and interleaved burst ordering

•

Programs internal control for ZQ short calibration cycles for DDR3 configurations

•

Supports dynamic scheduling to optimize bandwidth and latency

•

Supports self refresh entry and exit on command

•

Supports deep power-down entry and exit on command

•

Flexible address mapper logic to allow application specific mapping of row, column, bank, and rank

bits

•

Configurable support for 1T or 2T timing on the DDR SDRAM control signals

•

Supports autonomous DRAM power-down entry and exit caused by lack of transaction arrival for

programmable time

•

Advanced power-saving design includes toggling of command, address, and data pins

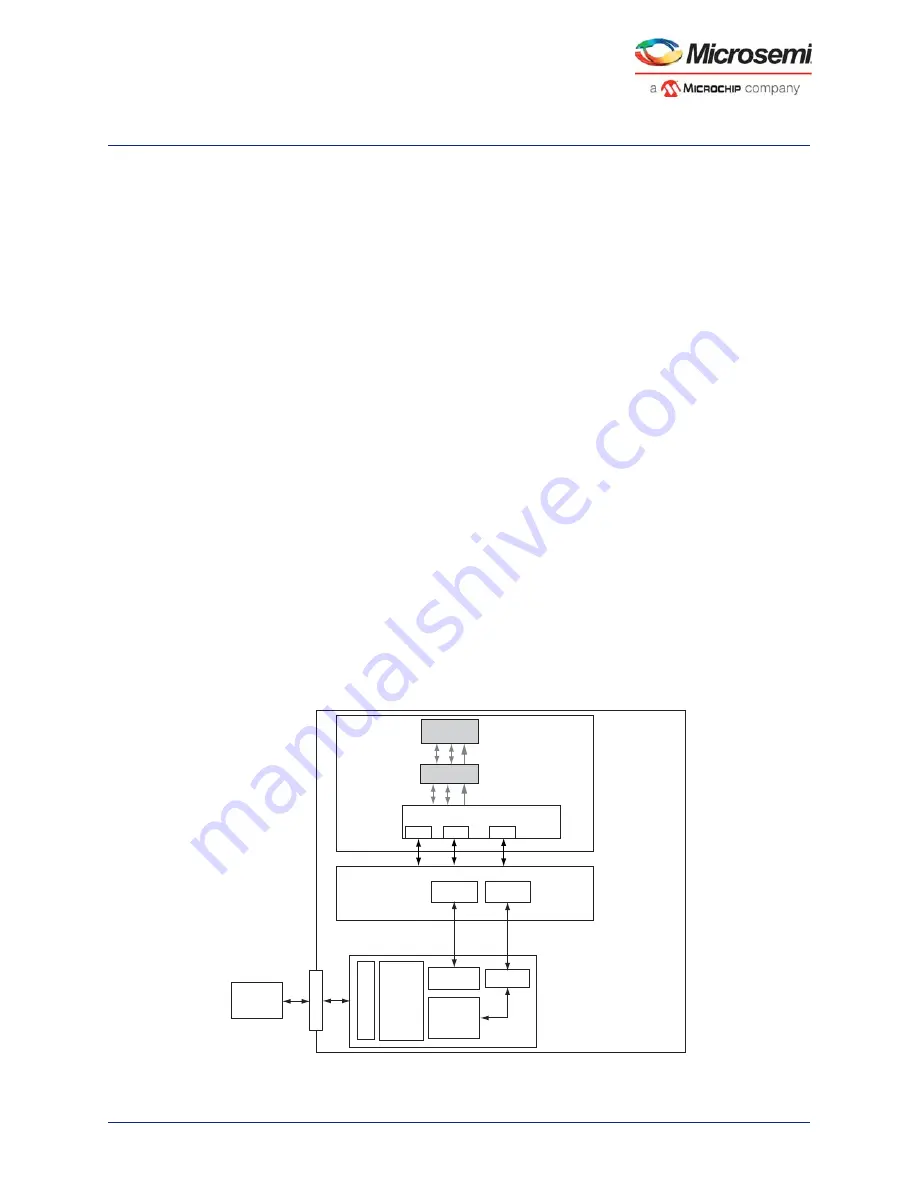

The system level block diagram of the FDDR subsystem is shown in the following illustration.

Figure 74 •

System Level FDDR Block Diagram

AHB Bus Matrix

Fabric

FDDR

SmartFusion2/IGLOO2

MSS/HPMS

DDR_FIC

AXI

Transaction

Controller

APB

Master

16-Bit APB

DDR

SDRAM

DDR

Controller

APB Config

Register

64-Bit AXI/

Single 32-Bit AHBL/

Dual 32-Bit AHBL

Note:

Blocks and arrows marked in grey, only in SmartFusion2 MSS. Rest are all similar in MSSHPMS.

AXI/AHB

Master

FIC_0

FIC_2

ARM Cortex-M3

Processor

S D I

Cache Controller

S D IC

FIC_1

D

D

R

P

H

Y

D

D

R

I

O