DDR Bridge

Microsemi Proprietary UG0446 User Guide Revision 7.0

209

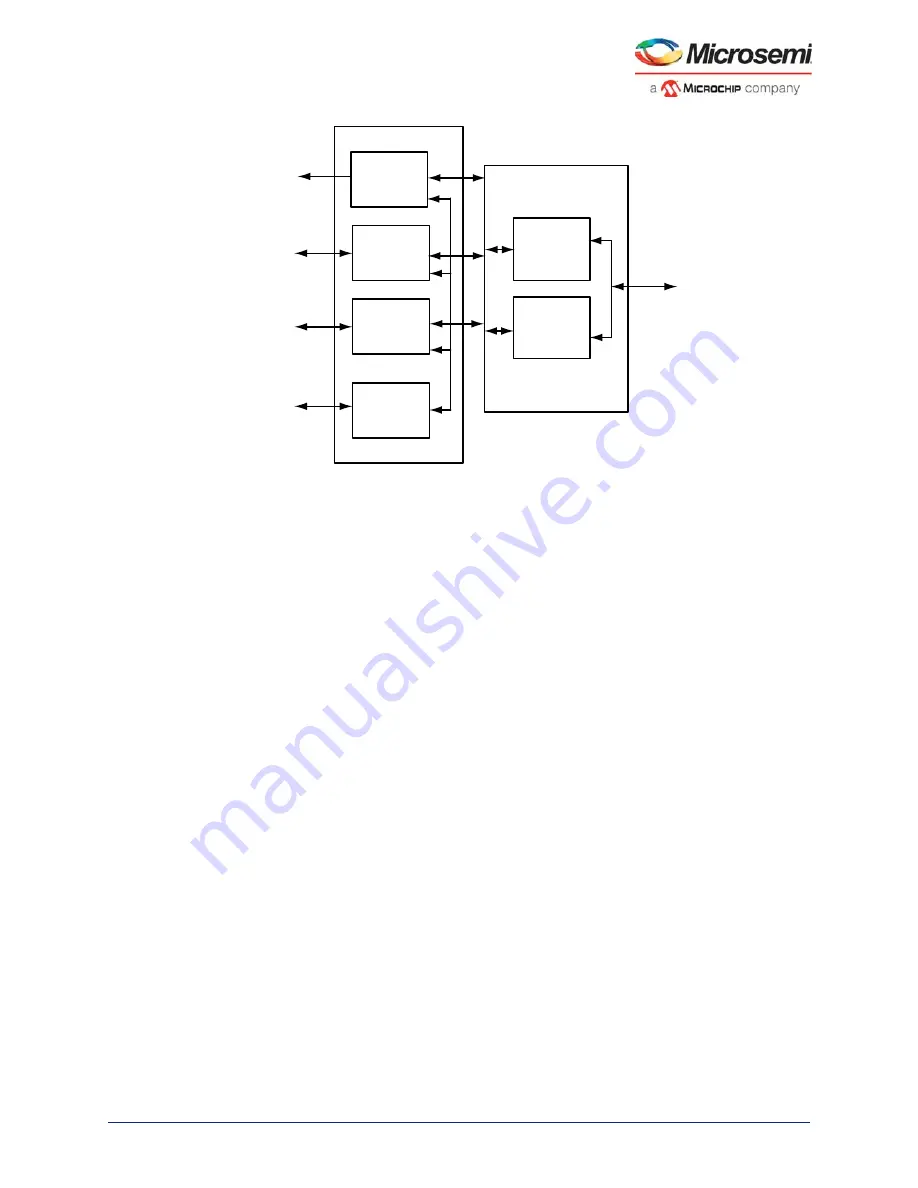

Figure 128 •

DDR Bridge Functional Block Diagram

Arbitration between the four AHB interfaces is handled as follows:

•

Fixed priority between AHB Interfaces 0 and 1, with 0 having the highest priority

•

Round robin arbitration between interfaces 2 and 3

5.1.2

Details of Operation

This section provides a functional description of each block in the DDR Bridge, as shown in the previous

illustration.

5.1.2.1

Write Combining Buffer

The write combining buffer (WCB) combines multiple write transactions from the AHB master into AXI

burst transactions. The WCB has a user configurable burst size of 16 or 32 bytes. Each WCB maintains

a base address tag that stores the base address of the data to be combined in the buffer.

For each write transaction, the address is compared with the WCB tag. If the address matches the tag,

data is combined into the buffer. The WCB writes to the correct byte location based on the offset address

of the data. WCB can also be disabled, if buffering is not required.

The WCB has a 10-bit timer (down counter), which starts when the first bufferable write data is loaded

into the WCB. The timer starts decrementing its value at every positive edge of the AHB clock and when

it reaches zero, the data in the WCB is written to the AXI slave.

The WCB checks for any other master that has initiated a read to the same address for which data is

already present in a write buffer or for which a write operation is ongoing. If the address for a read

request matches the write buffer tag, the read request is held until the buffer is written completely to the

AXI slave.

the following illustration shows the flowchart for WCB operation.

Read

Read

Buffer

Buffer

Write Access

rite Access

Control

Control

Read Access

Read Access

Control

Control

WCB and Read

and Read

Buffer

Buffer

AHB Interface 0 to

e 0 to

connect with AHB Master

connect with AHB Master

AHB Interface 1 to

e 1 to

connect with AHB Master

connect with AHB Master

Arbiter

To AXI Slave

WCB and Read

and Read

Buffer

Buffer

WCB and Read

and Read

Buffer

Buffer

AHB Interface 2 to

e 2 to

connect with AHB Master

connect with AHB Master

AHB Interface 3 to

e 3 to

connect with AHB Master

connect with AHB Master