Soft Memory Controller Fabric Interface Controller

Microsemi Proprietary UG0446 User Guide Revision 7.0

220

6.1

Functional Description

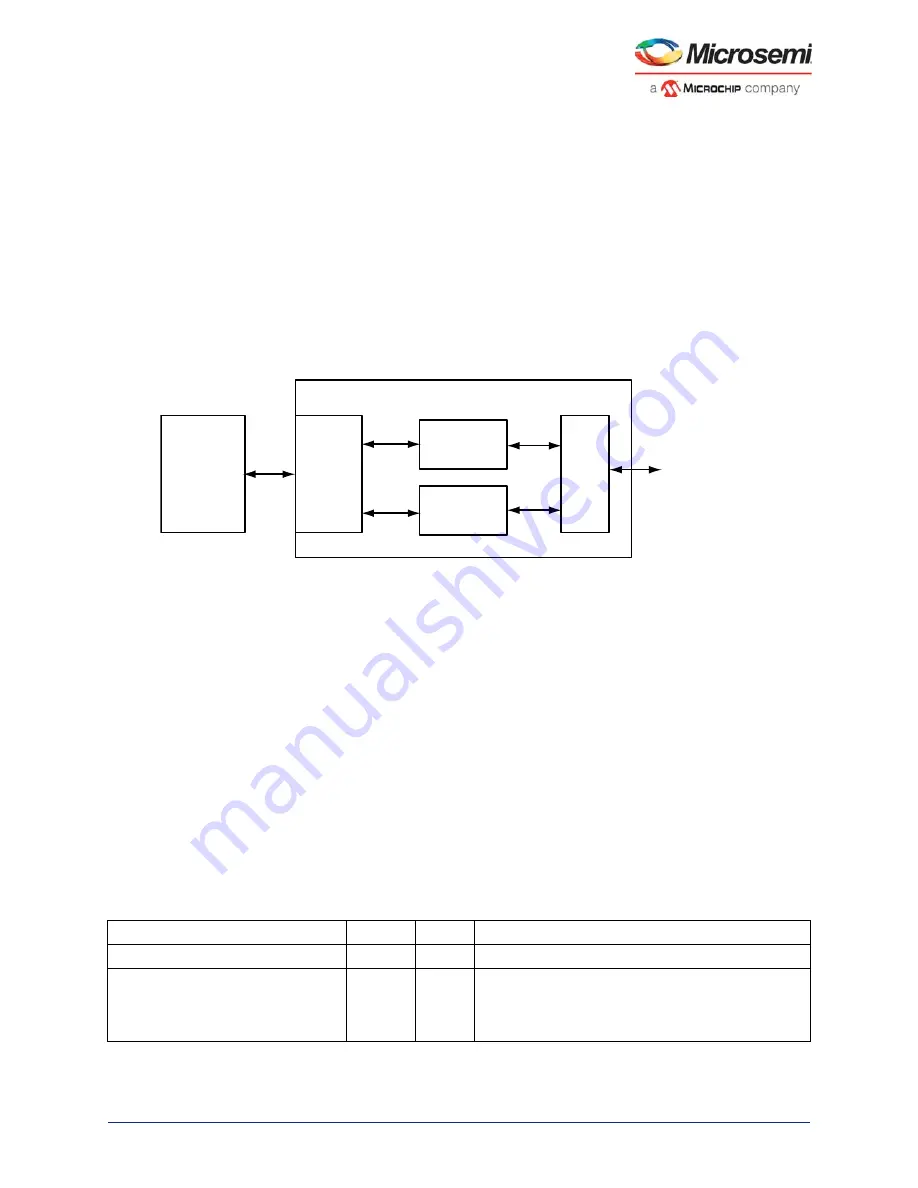

The SMC_FIC receives 64-bit AXI transactions from the MSS/HPMS DDR bridge and converts them into

64-bit AXI or 32-bit AHB-Lite transactions to the SMC in the FPGA fabric. The following illustration shows

the block diagram of the SMC_FIC. The SMC_FIC has two bridges:

•

The AXI-AHB bridge converts 64-bit AXI transactions into 32-bit AHB transactions. It implements the

AXI master to AHBL master protocol translator. This bridge is enabled when the SMC_FIC is

configured for a 32-bit AHB interface.

•

The AXI-AXI bridge facilitates 64-bit AXI transactions from the MSS/HPMS DDR bridge to the 64-bit

AXI FPGA fabric interface. This bridge is enabled when the SMC_FIC is configured for a 64-bit AXI

interface.

The SMC_FIC receives a clock from the MSS/HPMS CCC that is identical to M3_CLK/HPMS_CLK.

HPMS peripherals can access the external memory with the address space 0xA0000000 to

0xD0000000.

Figure 139 •

SMC_FIC Block Diagram

Note:

The Libero 11.2 System Builder configures the SMC_FIC in AHB mode for the devices M2GL005,

M2GL010, and M2GL025. For other devices it configures the SMC_FIC in AXI mode.

6.1.1

Port List

The following two tables show the 64-bit AXI and 32-bit AHBL port lists.

Note:

The SMC_FIC in M2S005, M2S010, M2S025, M2GL005, M2GL010, and M2GL025 devices provides

only one 32-bit AHB-Lite interface.

The AXI interface has the following limitations:

•

Supports only 64-bit read/write transactions on the AXI slave interface.

•

Exclusive access cycles are not supported

The SMC_AXI FIC AXI Read transactions can only be any of the following:

•

Single transfer of 64 bit only aligned to 64-bit addresses.

•

Wrap Transactions of 64-bit size and Wrap burst length of 2 which are aligned to 128-bit (16 byte)

addresses.

•

Wrap Transactions of 64-bit size and Wrap burst length of 4 which are aligned to 256-bit (32 byte)

addresses.

Table 166 •

SMC_FIC 64-bit AXI Port List

Signal

Direction Polarity Description

MDDR_SMC_AXI_M_WLAST

Output

High

Indicates the last transfer in a write burst.

MDDR_SMC_AXI_M_WVALID

Output

High

Indicates whether or not valid write data and strobes

are available.

1: Write data and strobes available

0: Write data and strobes not available

AXI-AHB

Bridge

AXI-AXI

Bridge

MUX

AXI

AXI

AHB

AXI

MSS/HPMS

DDR Bridge

64-Bit

AXI

SMC_FIC

64-Bit

AXI Slave

Interface

64-Bit AXI/

32-Bit AHBL

Master Interface